# **DSP PRODUCTS DATABOOK**

DSP MICROPROCESSORS MICROCODED SUPPORT COMPONENTS FLOATING POINT COMPONENTS FIXED POINT COMPONENTS

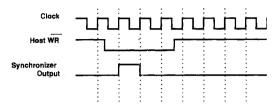

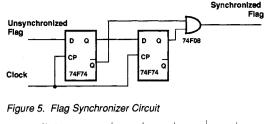

# How to Find Product Data in This Databook

# THIS VOLUME

Contains Data Sheets, Selection Guides, Application Notes, and a wealth of background information on components for number crunching and digital signal processing (DSP).

It is one member of a three-volume, 2,000-page set of Databooks describing and specifying Linear, Conversion, and DSP products from Analog Devices, Inc., in IC, hybrid, and assembled form for measurement, control, and real-world signal processing.

# IF YOU KNOW THE MODEL NUMBER

Turn to the product index on inside back cover at the back of the book and look up the model number. You will find the Section-Page location of data sheets bound into this volume.

If you're looking for a form-and-function-compatible version of a product originally brought to market by some other manufacturer (second source), add our "ADSP" prefix and look it up in the index.

# IF YOU DON'T KNOW THE MODEL NUMBER

Find your function in the list on the opposite page or in the Table of Contents on pages 1–5 and 1–6. Turn directly to the appropriate Section. You will find a functional Selection Guide at the beginning of the Section. The Selection Guides will help you find the products that are the closest to satisfying your need. Use them to compare all products in the category by salient criteria.

# IF YOU CAN'T FIND IT HERE . . . ASK!

If it's not a DSP product, it's probably in one of the two sister volumes, the *Linear Products Databook* or the *Data Conversion Products Databook*. If you don't already own these volumes, you can have them FREE by getting in touch with Analog Devices or the nearest sales office, or phoning (617)-329-4700, Extension 3392.

See Worldwide Service Directory on pages 8-6 and 8-7 at the back of this volume for our sales-office phone numbers.

# **Contents of Other Databooks**

# DATA CONVERSION PRODUCTS DATABOOK

D/A Converters A/D Converters Data Acquisition Subsystems V/F Converters F/V Converters Sample-Track/Hold Amplifiers Voltage References Multiplexers and Switches Synchro/Resolver Converters Application Specific ICs Power Supplies

# LINEAR PRODUCTS DATABOOK

Operational Amplifiers Instrumentation Amplifiers Isolation Amplifiers Temperature Measurement Components RMS-to-DC Converters Digital Panel Instruments Multipliers/Dividers Log/Antilog Amplifiers Special Function Components Comparators Temperature Transducers Signal Conditioning Components & Subsystems Application Specific ICs Power Supplies

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Specifications shown in this Databook are subject to change without notice.

| 1 | <b>General Information</b>    |

|---|-------------------------------|

| 2 | <b>DSP Microprocessors</b>    |

| 3 | Microcoded Support Components |

| 4 | Floating-Point Components     |

| 5 | <b>Fixed-Point Components</b> |

| 6 | Package Information           |

| 7 | Application Notes             |

| 8 | Appendix                      |

|   |                               |

# 1987 DSP Products Databook

©Analog Devices, Inc., 1987 All Rights Reserved

.

# General Information Contents

1

|                      | Page  |

|----------------------|-------|

| General Introduction | 1 – 3 |

| Table of Contents    | 1 – 5 |

1–2 GENERAL INFORMATION

# Introduction

#### ANALOG DEVICES

Analog Devices is the industry's leading supplier of highperformance signal processing integrated circuits. Since 1965, when we introduced innovative modular op amps, we have consistently advanced the state of the art in components technology. Today, with 80% of our sales generated by integrated circuits, we have the industry's most widely recognized line of advanced signal processing chips. Our strengths include proprietary wafer fabrication processing technologies, outstanding product quality, strong internal manufacturing, and innovative, high-performance product architectures.

# THE GROWING IMPORTANCE OF DSP

While signal processing was an exclusively analog phenomenon in the early 1970s, it is increasingly performed in the digital domain. Signals from the real world are digitized and fed to a digital signal processing (DSP) subsystem where fast arithmetic processors allow operations such as filtering and spectral analysis to be performed at real-time rates.

# THE ROLE OF DSP AT ANALOG DEVICES

As the leader in signal processing circuit technology, Analog Devices was quick to recognize the important opportunities made possible by DSP. Our customer base spans a wide area, including instrumentation, defense/avionics, scientific computing, industrial, medical, and telecommunications. These areas have in common the need to continually advance the performance of their systems. Increasingly they have turned to fast numbercrunching digital hardware to complement their analog processing. A key strategy of Analog Devices is to offer customers the industry's best family of high-performance signal processing devices – ranging from those strictly in the analog domain, to converters, to high-speed digital processors.

#### THE DSP DIVISION

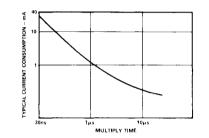

Analog Devices was first in the industry to bring CMOS semiconductor technology to the area of fast arithmetic processors. In 1983, our DSP Division introduced a set of seven CMOS fixed-point multipliers that matched the speed of bipolar alternatives, while cutting power requirements by a factor of twenty. This breakthrough redirected the focus of the industry from bipolar to CMOS for high-speed VLSI circuits.

Our innovations in CMOS wafer fabrication technology continued as we pushed processing geometries from the  $5\mu$ m level down to 1.5 $\mu$ m. In parallel, we brought out a complete building block family of VLSI processors for high-end DSP and numeric processing systems including a 64-bit IEEE floating-point chipset, the ADSP-3210 and ADSP-3220. We again advanced the state of the art in DSP with the introduction of the industry's first microprocessor optimized for DSP, the ADSP-2100.

# ANALOG DEVICES' DSP CAPABILITIES

Currently the DSP Division is in production with a  $1.5\mu m$  double-layer metal CMOS process. We are now moving to a

1.0 $\mu$ m CMOS process, continuing our innovation in process technology. Analog Devices continues to develop advanced processes (such as a specialized bipolar process and gallium arsenide) both internally and through strategic investments. For example, we recently introduced our first bipolar DSP product, a 16 × 16 multiplier that operates at cycle times in excess of 50MHz.

During 1986 we brought on-line a new VLSI wafer fabrication module to handle the volumes and advanced geometries of our DSP product line. Our assembly facilities include factories in Wilmington, Massachusetts and the Philippines. Our VLSI test capability is located in Norwood, Massachusetts, the Division's headquarters.

Analog Devices supports its DSP products with a technically strong direct salesforce and readily available applications assistance. Included in our applications support is a quarterly newsletter -DSPatch – that brings you up-to-date applications information on our products and on the general field of DSP. If you're not already receiving *DSPatch*, call or write us.

## DSP PRODUCTS DATABOOK

This book provides complete technical data on DSP products from Analog Devices. Included are:

- Comprehensive Data Sheets on some 20 significant product families

- Selection Guides for rapid product finding

- DSP Application Notes

- List of available Technical Publications on real-world analog and digital signal processing

- Worldwide Service Directory

- Index.

Besides this Databook, the present series includes a Linear Products Databook and a Data Conversion Products Databook; like this book, both are available free upon request.

#### TECHNICAL SUPPORT

Our extensive technical literature discusses the technology and applications of products for precision measurement and control. Besides tutorial material and comprehensive data sheets, including a large amount in our Databooks, we offer Application Notes, Application Guides, Technical Handbooks (at reasonable prices), and several serial publications; for example, *Analog Productlog* provides brief information on new products being introduced, and *Analog Dialogue*, our technical magazine, provides in-depth discussions of new developments in analog and digital circuit technology as applied to data acquisition, signal processing, control, and test. We maintain a mailing list of engineers, scientists, and technicians with a serious interest in our products. In addition to Databook catalogs, we also publish several short-form catalogs on specific product families. You will find typical publications described on pages 8-2 and 8-3 at the back of the book.

### SALES OFFICES

Backing up our design and manufacturing capabilities and our extensive array of publications is a network of sales offices and representatives throughout the United States and most of the world. They are staffed by experienced sales and applications engineers, and many of them maintain a local stock of Analog Devices products. Our Worldwide Service Directory, as of the publication date, appears on pages 8-6 and 8-7 at the back of the book.

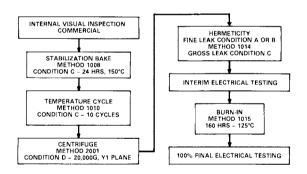

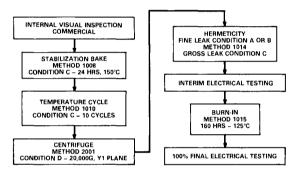

#### RELIABILITY

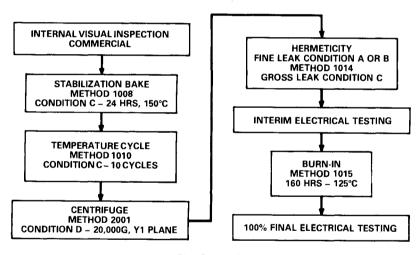

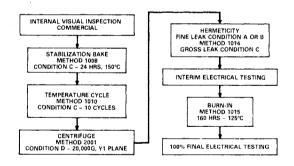

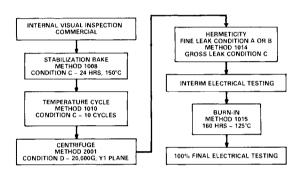

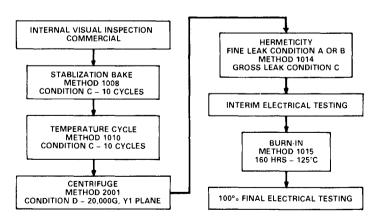

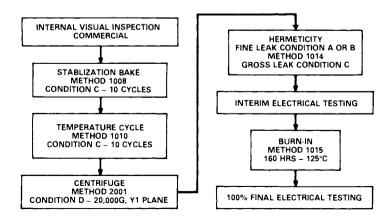

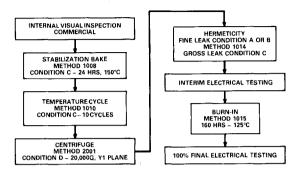

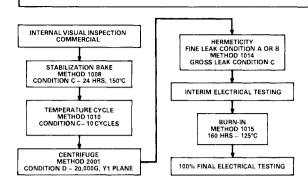

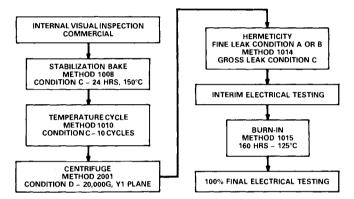

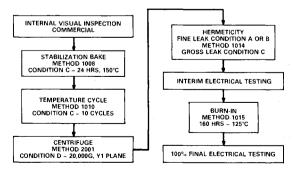

The manufacture of reliable products is a key objective at Analog Devices. We maintain facilities that have been qualified under such standards as MIL-M-38510 for ICs in the U.S. and Ireland and MIL-STD-1772 for hybrids. More than 20 of our products both proprietary and second-source—have qualified for JAN part numbers; others are in the process. Most of our ICs are available in versions that comply with MIL-STD-883C Class B. We publish a *Military Products Databook* for designers who specify ICs and hybrids for military contracts (the 1987 issue contains data on nearly 150 available product families). A newsletter, *Analog Briefings*, provides current information about the status of reliability at ADI.

Our PLUS program makes available standard devices (commercial and industrial grades, plastic or ceramic packaging) for *any* user with demanding application environments, at a small premium. Subjected to stringent screening, similar to MIL-STD-883 test methods, they are often suffixed "/+" and are available from stock.

#### PRICES

Accurate, up-to-date prices are an important consideration in making a choice among the many available product families. Since prices are subject to change, current price lists and/or quotations are available upon request from our sales offices.

# **Table of Contents**

# Page

1

| DSP Microprocessors – Section 2                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction                                                                                                                                           |

| Selection Guide                                                                                                                                        |

| ADSP-2100                                                                                                                                              |

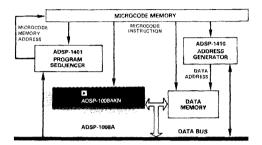

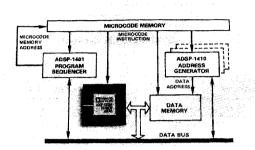

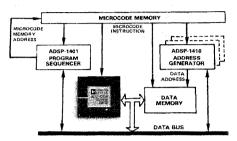

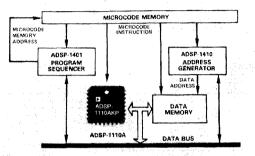

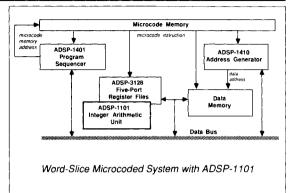

| Microcoded Support Component – Section 3                                                                                                               |

| Introduction                                                                                                                                           |

| Selection Guide                                                                                                                                        |

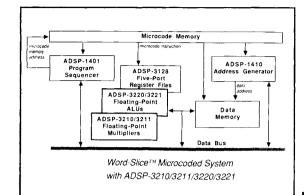

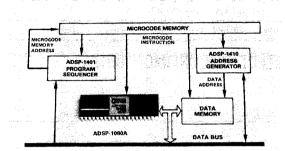

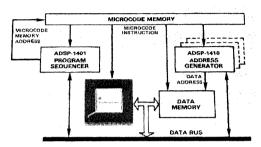

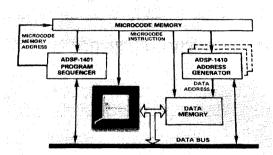

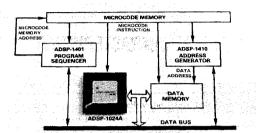

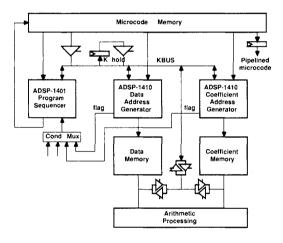

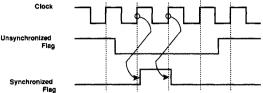

| ADSP-1401 – Word-Slice Program Sequencer                                                                                                               |

| ADSP-1410 – Word-Slice Address Generator                                                                                                               |

| Floating-Point Components – Section 4                                                                                                                  |

| Introduction                                                                                                                                           |

| Selection Guide $\ldots \ldots \ldots$ |

| ADSP-3210/ADSP-3211/ADSP-3220/ADSP-3221 – 64-Bit IEEE Floating-Point Chipsets                                                                          |

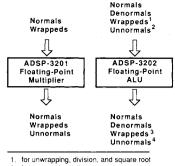

| ADSP-3201/ADSP-3202 – 32-Bit IEEE Floating-Point Chipsets                                                                                              |

| ADSP-3212/ADSP-3222 – 64-Bit IEEE Floating-Point Chipsets                                                                                              |

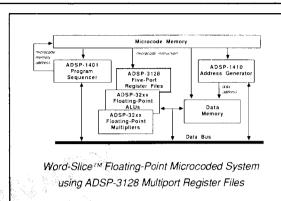

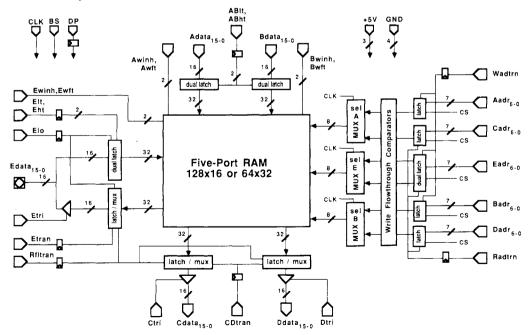

| ADSP-3128 – Multiport Register File                                                                                                                    |

| MD31-5128 - Multipolt Register 1 Id                                                                                                                    |

| Fixed-Point Components – Section 5                                                                                                                     |

| Introduction                                                                                                                                           |

| Selection Guide                                                                                                                                        |

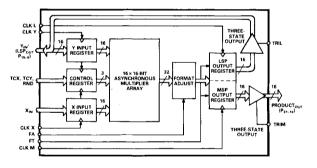

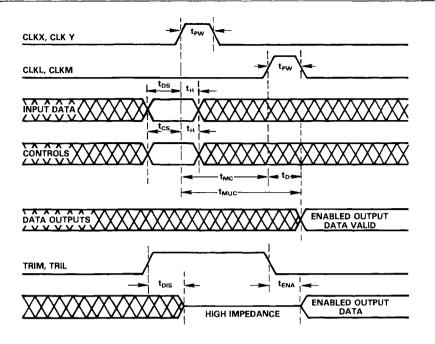

| Industry Standard Fixed-Point Components                                                                                                               |

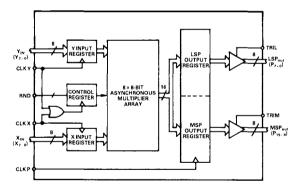

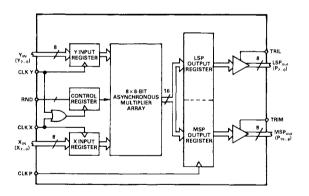

| ADSP-1080A – 8 × 8-Bit CMOS Multiplier                                                                                                                 |

| ADSP-1081A – 8 × 8-Bit Unsigned-Magnitude CMOS Multiplier                                                                                              |

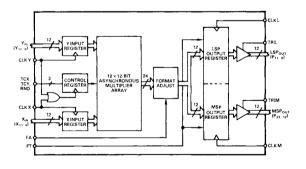

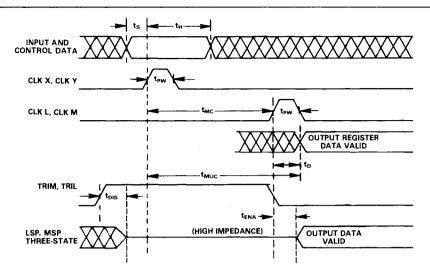

| ADSP-1012A – 12×12-Bit CMOS Multiplier                                                                                                                 |

| ADSP-1016A – 16 × 16-Bit CMOS Multiplier                                                                                                               |

| ADSP-1008A - 8 × 8-Bit CMOS Multiplier/Accumulator                                                                                                     |

| ADSP-1009A – 12×12-Bit CMOS Multiplier/Accumulator                                                                                                     |

| ADSP-1010A - 16×16-Bit CMOS Multiplier/Accumulator                                                                                                     |

| Enhanced Fixed-Point Components                                                                                                                        |

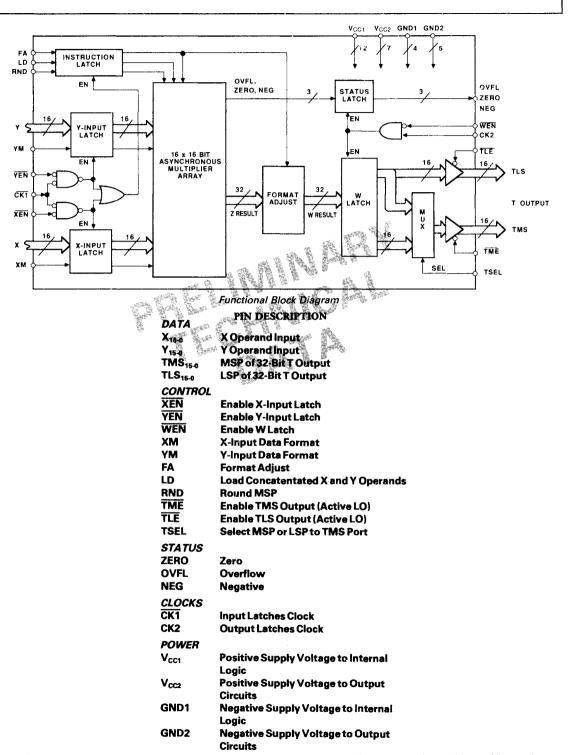

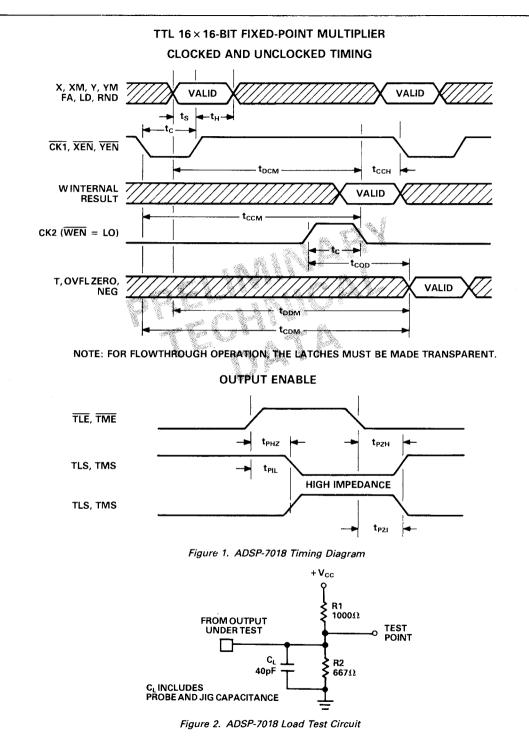

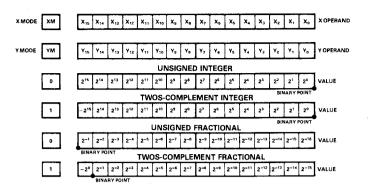

| ADSP-7018 – TTL 16×16-Bit Multiplier                                                                                                                   |

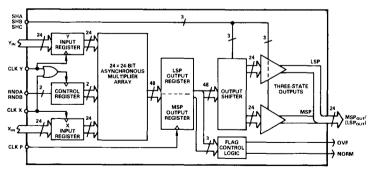

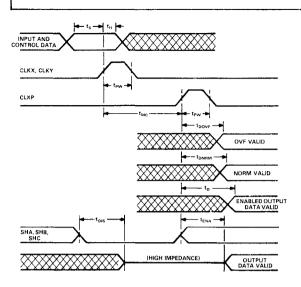

| ADSP-8018 – ECL 16×16-Bit Multiplier                                                                                                                   |

| ADSP-1024A – 24 × 24-Bit CMOS Multiplier                                                                                                               |

| ADSP-1110A – 16 × 16-Bit CMOS Single Port Multiplier/Accumulator                                                                                       |

| ADSP-1101 – 16-Bit Integer Arithmetic Unit                                                                                                             |

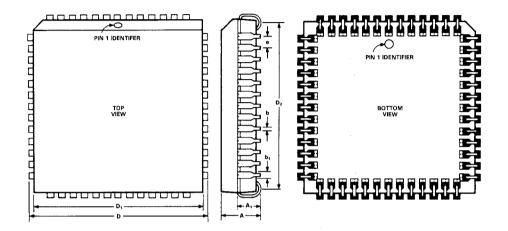

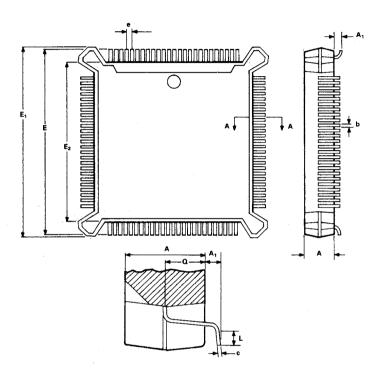

| Package Information – Section 6                                                                                                                        |

# Page

| <b>Application Notes – Section 7</b>                                              |

|-----------------------------------------------------------------------------------|

| Introduction                                                                      |

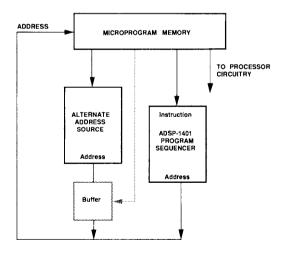

| Sharing the Output Bus of the ADSP-1401 Microprogram Sequencer                    |

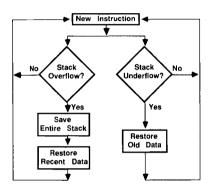

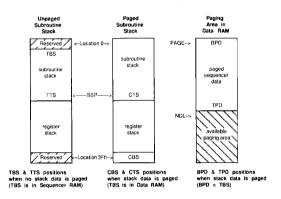

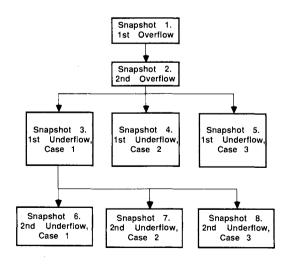

| Stack Paging Expands Internal Ram of the ADSP-1401 Program Sequencer              |

| Using the Counters of the ADSP-1401 Program Sequencer for Loop and Event Counting |

| Variable Width Bit-Reversing with the ADSP-1410 Address Generator                 |

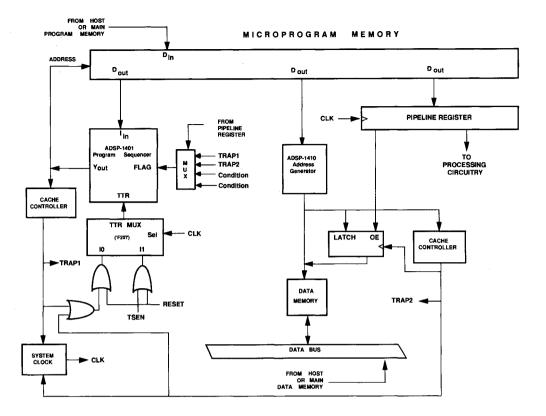

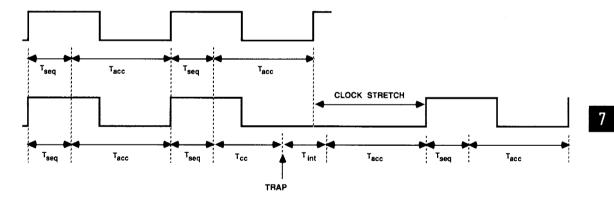

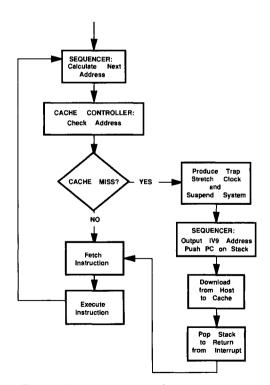

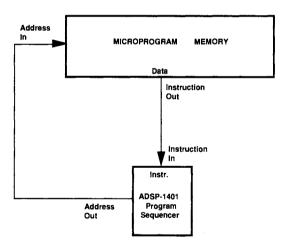

| Implement a Cache Memory in Your Word-Slice System                                |

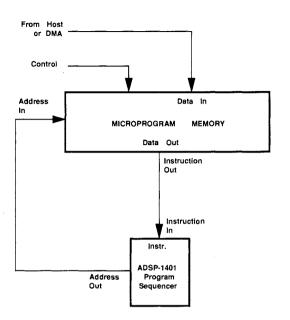

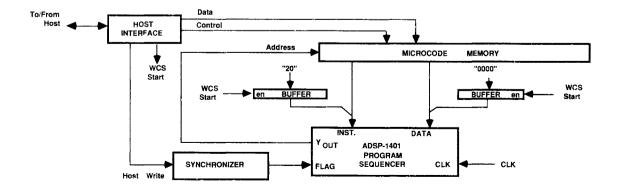

| Implement a Writeable Control Store in Your Word-Slice System                     |

| Optimize Data Transfers Between Word-Slice Components                             |

| A Guide to Designing Microcoded Circuits                                          |

| <b>Appendix – Section 8</b>                                                       |

| Technical Publications                                                            |

| Ordering Guide                                                                    |

| Worldwide Service Directory                                                       |

| Product Index                                                                     |

|                                                                                   |

# DSP Microprocessors Contents

|                 | Page   |

|-----------------|--------|

| Introduction    | 2 – 3  |

| Selection Guide | 2 – 13 |

| ADSP-2100       |        |

2–2 DSP Microprocessors

The ADSP-2100 is a single-chip processor optimized for digital signal processing (DSP) and other high-speed numeric processing applications. The chip has many special features which facilitate a fast design cycle. The ADSP-2100 offers:

# 1. Easy-to-Attain High Performance

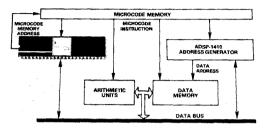

The ADSP-2100 integrates arithmetic/logic unit(ALU), multiplier/accumulator(MAC), barrel shifter, data address generators, and a program sequencer in a single device. Its architecture offers single-cycle access to both the external program and data memories. The resulting architecture combines the functions and performance of a bit-slice/building block system with the ease-of-design and development of a general-purpose microprocessor.

#### 2. Easy-to-Understand Instruction Set

The ADSP-2100 instruction set uses an algebraic syntax, similar to high-level languages, making it easy to write and understand code for the processor. This results in easier and faster code development and maintenance.

# 3. Easy-to-Use Development Tools

The complete set of development tools available for the ADSP-2100 (Cross-Software, Simulator, In-Circuit Emulator, and Evaluation Board) minimizes both design time and effort. Your application is up and running faster with this powerful development system.

#### 4. Easy-to-Design System Interface

The advanced design of the ADSP-2100 allows simple interconnection of memories and I/O devices, minimizes the external logic required to handle interrupts, and supports straightforward host interface and multiprocessing of multiple ADSP-2100s.

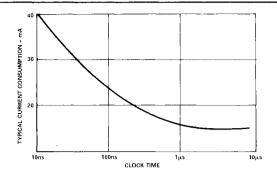

The ADSP-2100 is available in 6 or 8MHz versions and is fabricated in a high-speed 1.5 micron double-layer metal CMOS process. It dissipates less than 600mW. The part is available in both commercial and military versions.

Faster versions of the ADSP-2100 are planned. Check with your local sales office for current information.

Some of the applications for which the ADSP-2100 has been designed-in are image processing, speech processing, high-speed modems, telecommunications, radar, sonar, graphics, and numerical processing.

#### ADSP-2100 Benchmarks Algorithm Performance @ 8MHz FIR Filter 125ns per Tap (1 Cycle per Tap) Complex FIR Filter 500ns per Tap (4 Cycles per Tap) **Biquad Filter Section** 875ns per Section (71 Cycles per Section) Lattice Filter Section 625ns per Section (5 Cycles per Section) 1024-Point Complex 6.61ms FFT (Radix-2) 4096-Point Complex 33.3ms FFT (Radix-2)

| Feature                                                                                                       | Benefit                                                                                             |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Separate Program and Data Buses                                                                               | Efficient Data Transfer, in Parallel with Computations                                              |

| Dual Purpose Program Memory for Both Instruction<br>and Data Storage                                          | Dual Operand Fetch in One Cycle                                                                     |

| Single-Cycle Direct Access to Both Program and Data Memory                                                    | No Time Penalty for Off-Chip Memory Access                                                          |

| Single Cycle Instruction Execution with 125ns Cycle Time                                                      | High Throughput                                                                                     |

| Multifunction Instructions                                                                                    | High Degree of Parallelism                                                                          |

| Addresses 16K × 16 of Data Memory and 16K × 24 of Program<br>Memory (a 16K × 24 Expansion Available for Data) | Room for Complex Programs and Up to 32K of Data                                                     |

| Three Independent Computational Units (ALU, MAC, Barrel Shifter)                                              | Programming Flexibility; Output of Any Computational Unit<br>Can Be Input to Any Computational Unit |

| Two Independent Data Address Generators                                                                       | Dual Operand Fetch in One Cycle; No Overhead Modulo<br>Addressing; Bit-Reversing                    |

| Powerful Program Sequencer                                                                                    | Zero-Overhead Looping and Single-Cycle Conditional Branches                                         |

| Internal Instruction Cache                                                                                    | Three Bus Performance During Program Loops                                                          |

| Provisions for Multiprecision Computation and Saturation Logic                                                | Processing Flexibility                                                                              |

| Four External Interrupts                                                                                      | Easy System Design; Minimizes External Logic                                                        |

| Complete Development System                                                                                   | Ease of Program Development                                                                         |

| 1.5µm CMOS                                                                                                    | High-Speed and Low-Power Dissipation                                                                |

| Simple Bus Interface                                                                                          | Simplifies Interconnections of Memories and I/O Devices                                             |

| Bus Request and Bus Grant Signals                                                                             | Supports Multiprocessing of Several ADSP-2100s and Easy<br>Host Interface                           |

| Background Registers on All Computational Units                                                               | Fast Context Switching for Ease of Interrupt Handling                                               |

# **ADSP-2100 Features and Benefits**

# **ADSP-2100 Development System**

**FEATURES**

Cross-Software Modules: System Builder Assembler Linker PROM Splitter Simulator Stand-Alone In-Circuit Emulator Cross-Software Available for Use on IBM PC<sup>†</sup> Under PC-DOS<sup>†</sup> DEC VAX<sup>‡</sup> Under VMS<sup>‡</sup> Macros for Modular Code Development Interactive and Symbolic User-Friendly Interface Stand-Alone Evaluation Board

# GENERAL DESCRIPTION

The ADSP-2100 Development System is a complete set of development tools for systems using the ADSP-2100 DSP microprocessor. This powerful and easy-to-use set of tools is extremely valuable in implementing an ADSP-2100 system design: the software tools shorten the software design cycle and the Emulator and Evaluation Board facilitate the debug cycle.

The ADSP-2100 Development System includes:

A complete Cross-Software System consisting of five modules:

| <ul> <li>to define the target hardware<br/>environment</li> </ul>           |

|-----------------------------------------------------------------------------|

| - to assemble code/data modules                                             |

| <ul> <li>to link separately assembled<br/>modules</li> </ul>                |

| <ul> <li>to generate PROM burner<br/>compatible files</li> </ul>            |

| <ul> <li>to perform an instruction-level<br/>software simulation</li> </ul> |

|                                                                             |

- A stand-alone in-circuit hardware Emulator

- A stand-alone Evaluation Board

With the Cross-Software System, the user defines the target system, writes a program using the ADSP-2100 Assembly Language, assembles each program module; links all modules to form a running system, simulates execution of the code, and downloads the program into PROMs for hardware implementation. VAX VMS and IBM PC versions of the Cross-Software are available. The System Builder, Assembler, Linker, and PROM Splitter for the IBM PC are sold together in a single package, with the Simulator available separately. The VAX VMS version of the Cross-Software System is sold in a single package.

The In-Circuit Emulator provides the user with complete monitoring and control capabilities for debugging code in the actual target system. With its pod connected to the target system's ADSP-2100 socket, the Emulator operates at the processor's full cycle rate. Through the Emulator's RS-232 connections, the user can also download program files created with the Cross-Software Tools from the host computer system.

The ADSP-2100 Evaluation Board is an additional tool for evaluating the processor in real time and an aid to the development process. This board also provides analog I/O and an expansion port for user prototyping.

# ORDERING INFORMATION

Refer to Development System Selection Guide on page 2-13.

tIBM PC and PC-DOS are registered trademarks of International Business Machines Corp.

‡DEC VAX and VMS are trademarks of Digital Equipment Corp.

# ADSP-2100 Cross-Software Modules

**FEATURES**

Sustem Builder Allows the User to Specify Target Hardware Assembler Supports High-Level Constructs Supports Flexible Macro Processing Encourages Modular Code Development Provides a Full Range of Diagnostics Linker Supports Multi-Module Linking

Maps Assembler Output to Target Hardware

# GENERAL DESCRIPTION

The ADSP-2100 Cross-Software Modules allow the user to easily develop applications software for implementation on an ADSP-2100 system. The Cross-Software Modules include the following:

#### System Builder

The System Builder translates a user-defined description of the target hardware system into a form which can be utilized by other Cross-Software Modules. The ADSP-2100 Cross-Software Modules require knowledge of the target hardware system for the Linker to place relocatable segments, the Simulator to simulate external memory configurations, and for the PROM Splitter to generate separate program and data files. The user specifies the target program memory, data memory, and I/O port configurations by writing a System Specification Source File. The ADSP-2100 System Builder then translates this into an Architecture Description File which is read by the other ADSP-2100 Cross-Software Modules.

#### Assembler

The ADSP-2100 Assembler translates user-written source code modules into relocatable object-code modules. The user creates an assembler source code module by writing a program using the ADSP-2100 Assembly Language and defining variable data buffers and symbolic constants using the Assembler Directives. An assembly module becomes a "unit" of the complete system source code. Separately assembled object-code modules are linked together to form the final running system using the ADSP-2100 Linker.

# Linker

The ADSP-2100 Linker generates a complete executable program, the Program Memory/Data Memory Image File, by linking together object-code modules which were assembled separately. This output file is used by the Simulator, the PROM Splitter, and the Emulator. Another Linker output, the Debug Symbol Table File, contains a list of all symbols encountered by the Linker and enables the Simulator to utilize user-defined source code level symbols in its interface with the user.

## **PROM Splitter**

The ADSP-2100 PROM Splitter extracts the address information and the contents of the ROM portion of the PM/DM Image File and formats the extracted images for uploading to PROM burners. The PROM image file is generated in

**PROM Splitter**

Formats the ROM Memory Image for Uploading to PROM Burners Simulator Interactive User-Friendly Interface Full Symbolic Disassembly Simulates Hardware Configuration Simulates Port I/O Handling Flags Illegal Operations

either Motorola S Record, Intel Hex Record, or Daisy VLA format.

#### Simulator

The ADSP-2100 Simulator simulates the operation of the ADSP-2100 and allows the user to observe the contents of the 2100's registers, buses, stacks and program and data memories as a program is being executed. The Simulator is user-friendly, interactive, and screen-oriented. By utilizing the Architecture Description File output of the System Builder, the Simulator configures itself to match the target system hardware. The Simulator supports full symbolic disassembly via the Debug Symbol Table File output of the Linker.

The Simulator supports three execution modes:

- Emulator Mode, which runs at the fastest simulation speed and updates the screen every 256 cycles.

- Extend Mode, which updates the screen every cycle during program execution.

- Single Step Mode, which executes a single instruction per run command.

The Simulator has six major display modes:

- · Register Display, which displays the contents of the ADSP-2100 primary and alternate registers.

- Program Memory Display

- Data Memory Display

- Stack Display, which displays the contents of the ADSP-2100's program sequencer stacks.

- Trace Buffer Display, which displays the past external bus states of the ADSP-2100.

- Cache Memory Display

- In addition, the Simulator allows you to:

- Modify the contents of Registers, Program or Data Memory, or the Program Counter

- Set break points in program memory

- Set watch points in data memory

- Utilize command files

- Display user-defined addresses or values symbolically

- · Save and restore the state of the Simulator

- Dump program and data memory contents to files

- Patch, delete and execute code

- Utilize decimal or hexidecimal numeric format

- · Plot the contents of data memory on the terminal screen

# **ADSP-2100 Emulator**

FEATURES

Performs In-Circuit Emulation Operates at the Full Clock Rate of the ADSP-2100 (8MHz) Self-Emulation of Processor Same Interactive, Symbolic User Interface as the ADSP-2100 Simulator Multiple-Run Modes – Full Speed, Extend Mode or Single-Step Supports Breakpoints User Selectable Program Memory Source – Emulator or Target System User Selectable System Clock Source – Emulator, Target System, or External Two RS-232-C Connectors for Interfacing to a Host System and Terminal Optional Trace Board

# GENERAL DESCRIPTION

The ADSP-2100 Hardware Emulator is an In-Circuit Emulator which allows the user to debug code developed with the ADSP-2100 Cross-Software Modules in the actual target system. The Emulator, which utilizes an ADSP-2100 to selfemulate the processor, plugs into the target system's ADSP-2100 socket and operates at the ADSP-2100's cycle time.

The Emulator supports three execution modes:

- Emulator Mode, which runs at full processor speed.

- Extend Mode, which updates the screen every cycle during program execution.

- Single-Step Mode, which executes a single instruction per carriage return.

The Emulator has five major display modes:

- Register Display, which displays the contents of the ADSP-2100 primary and alternate registers.

- Program Memory Display

- Data Memory Display

- Stack Display, which displays the contents of the ADSP-2100's program counter stack.

- Trace Buffer Display (for optional Trace Board), which displays the past external bus states of the ADSP-2100.

With the same interactive, symbolic user interface as the ADSP-2100 Simulator, the Emulator allows the user to:

- Modify the contents of Registers, Program or Data Memory, or the Program Counter

- Set breakpoints in Emulator-based program memory

- Display user-defined addresses or values symbolically

- Patch, delete and execute code

- Utilize decimal or hexidecimal numeric format

In addition, the Emulator allows you to:

• Specify the baud rate and parity settings required by the user's terminal

- Activate or deactivate the Emulator Pod through software control

- Select the program memory source from either the Emulator's internally available Program Memory RAM or the target system's Program' Memory

- Download files from a host system

- Select the system clock source from either the Emulator's internal clock, the target system's clock or an external clock

# **ADSP-2100 Evaluation Board**

FEATURES

Stand-Alone ADSP-2100 System 125ns Cycle Time Operation 4K × 24 of Program Memory (with Sockets for Expansion to 32K) 2K × 16 of Data Memory (with Sockets for Expansion to 16K) Analog Interface via A Bidirectional Codec Channel Undedicated 12-Bit D/A Converter Microphone and Speaker Connections for Audio Applications

GENERAL DESCRIPTION

The ADSP-2100 Evaluation Board is an easy-to-use, low-cost way for evaluating the ADSP-2100 DSP Microprocessor in real-time applications. The ADSP-2100 Evaluation Board can play several different roles over the course of an ADSP-2100 design cycle:

• As a Real-time Demonstration System

The Evaluation Board allows the user to observe the ADSP-2100's real-time performance in executing standard DSP benchmarks.

• As a Real-time Evaluation System

The Evaluation Board can be utilized prior to design of proprietary hardware for the real-time execution of userdeveloped application routines.

• As a Simulation Accelerator

ADSP-2100 application code can be executed in real time for increased productivity of software developers.

The ADSP-2100 Evaluation Board is a stand-alone system and consists of an ADSP-2100 Digital Signal Microprocessor,  $4K \times 24$  of Program Memory, and  $2K \times 16$  of Data Memory. Additional program and data memory can be added as desired up to the full 32K program and 16K data memory address space via factory installed sockets.

A bidirectional codec channel and an undedicated 12-bit linear D/A converter allow for processing of real-world signals, and a prototyping expansion bus allows for customization to reflect the eventual hardware environment. In addition, four BNC Connectors are available for interfacing to external instrumentation. An integral microphone jack and input pre-amplifier, along with a speaker jack and output amplifier, allow for easy implementation of speech and telecommunication applications.

The Evaluation Board's ADSP-2100 runs under the control of an onboard host processor enabling the user to access a variety of powerful debugging tools. Interfacing to an external host computer system running the ADSP-2100 Cross Software (available in VAX/VMS and PC-DOS versions), the Evaluation Board serves as a valuable real-time development tool. The Evaluation Board connects to a terminal and host computer via two RS-232C serial connectors.

Four BNC Connectors Interfacing to External Instrumentation Expansion Port for Customization by User Same Interactive, Symbolic User Interface as the ADSP-2100 Emulator and Simulator Multiple Run Modes – Full Speed, Extend Mode or Single-Step Supports Breakpoints Two RS-232C Connectors for Interfacing to a Host System and Terminal

Utilizing the same user interface as the ADSP-2100 Emulator and Simulator, the Evaluation Board supports three execution modes:

- Emulator Mode, which runs at full processor speed.

- Extend Mode, which updates the screen every cycle during program execution.

- Single-Step Mode, which executes a single instruction per carriage return.

The Evaluation board has four major display modes:

- Register Display, which displays the contents of the ADSP-2100's primary and alternate registers.

- Program Memory Display.

- Data Memory Display.

- Stack Display, which displays the contents of the ADSP-2100's program counter stack.

The Evaluation Board allows the user to:

- Download ADSP-2100 Cross-Software generated executable code from a host computer.

- Modify the contents of Registers, Program or Data Memory, or the Program Counter.

- Set breakpoints in Program Memory.

- Display user-defined addresses or values symbolically.

- Patch, delete, and execute code.

The Evaluation Board requires an external  $\pm 12$  and  $\pm 5$  volt power supply (not included).

# ADSP-2100 User's Manual

This manual provides the information necessary for an engineer to understand the operation of the ADSP-2100 and to write programs for the ADSP-2100. Together with the ADSP-2100 data sheet, the manual provides all the information required to design a hardware system with the ADSP-2100.

| Chapter | Topic                    | Summary                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Overview                 | Overview of the ADSP-2100 and its development system.                                                                                                                                                                                                                                                                                                                                                               |

| 2       | Internal<br>Architecture | Describes the overall architecture and<br>functional relationships of the major<br>units. The internal operation of each<br>functional unit is described in detail:<br>the arithmetic/logic unit (ALU), the<br>multiplier/accumulator (MAC), the<br>barrel shifter, the data address<br>generator, the program sequencer, the<br>instruction cache and the program-data<br>(PMD-DMD) bus exchange.                  |

| 3       | System<br>Interface      | Discusses all major interfaces to the<br>ADSP-2100: the program memory<br>(PM) interface, the data memory<br>(DM) interface, the control interface<br>and the interrupt lines. This chapter<br>gives a functional description of the<br>interfaces and their sequences of oper-<br>ation. For actual timing parameters,<br>refer to the ADSP-2100 data sheet.<br>The pin descriptions are given in this<br>chapter. |

| 4       | Instruction<br>Set       | Organized as a reference section. All<br>instructions are grouped by major<br>type. These major groups (for example,<br>ALU, MAC, or MULTIFUNCTION)<br>are used as thumb heads in this chapter.<br>The operation and assembly syntax of<br>each instruction is fully described.                                                                                                                                     |

| A       | Instruction<br>Codes     | Shows the actual 24-bit instruction coding of each instruction.                                                                                                                                                                                                                                                                                                                                                     |

# ADSP-2100 Cross-Software Manual

This manual guides the engineer in the use of the ADSP-2100 Cross-Software on either the VAX/VMS, or the IBM PC or PC compatible.

| Chapter | Topic                  | Summary                                                                                                                                                               |

|---------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Overview               | Overview of the ADSP-2100 Cross-<br>Software System.                                                                                                                  |

| 2       | System<br>Builder      | Describes the System Builder, showing<br>its input and output files and describing<br>its syntax, operation, and error<br>messages.                                   |

| 3       | Assembler              | Describes the Assembler, showing its<br>input and output files and describing<br>the Assembler directives, operation<br>and error messages.                           |

| 4       | Linker                 | Describes the Linker, showing its<br>input and output files and describing<br>its operation and error messages.                                                       |

| 5       | Simulator              | Describes the Simulator. The complete<br>set of interactive commands and typical<br>displays is shown. The Simulator<br>provides on-line help for additional<br>help. |

| Α       | File Format            | Contains the file format for all input<br>and output files used by the Cross-<br>Software System.                                                                     |

| В       | System<br>Requirements | List the hardware and software re-<br>quirements for the computer systems<br>that can host the Cross-Software<br>System.                                              |

# ADSP-2100 Emulator Manual

This manual guides the engineer in the use of the ADSP-2100 Emulator with the target hardware designed for the specific application.

| Chapter | Торіс                                                           | Summary                                                                                                                                                   |

|---------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Overview                                                        | Overview of the ADSP-2100<br>Emulator.                                                                                                                    |

| 2       | Installation                                                    | Describes the installation procedure and $I/O$ connections (RS-232 and BNC).                                                                              |

| 3       | Configuration                                                   | Describes the initial configuration<br>of the Emulator such as setting the<br>baud rates for communications<br>and activating the ADSP-2100<br>processor. |

| 4       | Operation                                                       | Describes the Emulator's basic<br>operation and error messages,<br>highlighting the differences between<br>the Emulator and Simulator.                    |

| 5       | Development<br>Examples                                         | Contains step-by-step examples of Emulator sessions.                                                                                                      |

| A       | Specifications                                                  | Contains the specifications of the Emulator.                                                                                                              |

| В       | Timing<br>Comparison                                            | Compares the timing of the ADSP-2100 in the Emulator with that of an ADSP-2100 running in a non-Emulator system.                                          |

| С       | Accessing more<br>than 16K of<br>Target-Based<br>Program Memory | Tells how to use the Emulator<br>with more than 16K of<br>program memory in your<br>target system.                                                        |

| D       | Pin Diagrams                                                    | Shows the pin arrangement of the ADSP-2100.                                                                                                               |

| Е       | Replace Emulator<br>Hardware                                    | Describes how to replace Emulator<br>PROMS, pod board<br>and ADSP-2100 chip.                                                                              |

| F       | Terminal<br>Emulation<br>Software                               | Provides information about<br>specific terminal emulation<br>software that can be used<br>with the emulator                                               |

# ADSP-2100 Applications Handbook Volume 1

The ADSP-2100 Applications Handbook covers a wide variety of examples of numerical and digital signal-processing algorithms. Each Chapter contains an overview of the chapter topic and then follows with specific examples, including complete ADSP-2100 programs.

| Chapter | Торіс                        | Summary                                                                                                                                                                                                                                                  |

|---------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Introduction                 | Introduction to the Handbook.                                                                                                                                                                                                                            |

| 2       | Fixed Point<br>Arithmetic    | Describes using the ADSP-2100 for fixed-point single and multiprecision arithmetic.                                                                                                                                                                      |

| 3       | Floating Point<br>Arithmetic | Covers block floating point and full<br>floating point arthitmetic, and fixed-to-<br>floating and floating-to-fixed<br>conversions.                                                                                                                      |

| 4       | Function Approximation       | Covers function approximation, in-<br>cluding sine, arctangent, square root,<br>and logarithm. Uniform random<br>number generation is also described.                                                                                                    |

| 5       | Digital Filters              | Describes fixed coefficient digital<br>filters including single and double<br>precision FIR filters, two-dimensional<br>FIR filters, and complex FIR filters.<br>Also covered are direct form and<br>cascaded biquad IIR filters and lattice<br>filters. |

| 6       | FFTs                         | Covers Fast Fourier Transforms, both<br>radix-2 and radix-4. There are also<br>examples of both decimation-in-time<br>and decimation-in-frequency<br>algorithms. Windowing, bit reversal<br>and magnitude and phase are also<br>described.               |

| 7       | Adaptive<br>Filters          | Describes adaptive filtering using a single- or double-precision stochastic gradient algorithm.                                                                                                                                                          |

| 8       | Image<br>Processing          | Describes several image processing<br>algorithms including two-dimensional<br>convolutions, matrix multiplications<br>and histograms.                                                                                                                    |

| 9       | Speech<br>Algorithms         | Describes a number of linear predictive<br>speech coding algorithms including<br>linear predictive coding, auto and<br>cross correlation, Levinson recursion,<br>and pitch detection. A linear predictive<br>coding synthesizer is also described.       |

| 10      | Modems                       | Describes several algorithms used with<br>high-speed modems including the<br>complex-valued gradient and the<br>weighted Euclidean Distance.                                                                                                             |

### ADSP-2100 Training Course

This intensive three day workshop familiarizes participants with the features and capabilities of the ADSP-2100 digital signal microprocessor and its associated development tools. Each topic is discussed thoroughly and illustrated with practical examples. Hands-on laboratory exercises with individualized instruction are an integral part of the workshop. Because of the intensive nature of the workshop, participants will gain the most from it if they are already familiar with the general concepts of programming in any high level or assembly language.

The workshop begins with an introduction to the system architecture and terminology, followed by an in-depth discussion of the major functional units of the processor. Next, interfacing the ADSP-2100 to other circuits is considered. The instruction set is described in detail, with an opportunity to use the Simulator to observe the data flow and operating units. Several examples of arithmetic using different data formats help illustrate simple ADSP-2100 programs.

A large portion of the Workshop is devoted to seeing how the ADSP-2100 can be used in actual applications. Examples used include several types of filters, Fast Fourier Transforms and matrix operations. Although the course does not teach digital signal processing theory, each example is presented by first reviewing the general features of the algorithm, discussing its programming requirements, and finally tracing the operation of a sample program using the Simulator. After examining the available development tools, participants will have an opportunity to experiment with the programming of the ADSP-2100 either with predefined exercises or with problems they have brought to class.

This workshop will be a detailed and practical experience for anyone who will use the ADSP-2100. The price includes tuition, workshop materials, and the use of the development stations for laboratory exercises. Class size is limited to a maximum of fifteen to facilitate individual instruction and a practical hands-on experience.

Please call the Analog Devices Training Coordinator at (617) 461-3622 for an current schedule of workshops, a complete workshop brochure, and pricing.

#### ADSP-2100 Software Model for Board-Level Simulation

A behavioral model of the ADSP-2100 for use in software simulations of board or system-level products is available from Logic Automation of Beaverton, Oregon. The behavioral model, called a SmartModel\*, permits engineers to analyze their designs at a system level with a workstation and a logic simulator. The ability to proceed directly from the simulated design to the final product eliminates costly and time-consuming prototypes and multiple design revisions. Every SmartModel has extensive error checking capabilities. When it detects an error during a simulation, the model describes the type of error and when it occurred. Analog Devices has provided technical data on the ADSP-2100 to Logic Automation. The model has been validated with Analog Devices' production test vectors, insuring its correctness. SmartModels work on a variety of simulators, including Mentor Graphics. For more information, contact Logic Automation, Inc., Sales Engineering, P.O. Box 310, 19545 N.W. Von Neuman Dr., Beaverton, Oregon 97075, (503) 690-6900.

#### **Board Level ADSP-2100 Products**

The Industrial Automation Division of Analog Devices offers two board level products which incorporate the ADSP-2100. The RTI-680 is a VME board and the RTI-980 is a Multibus II board. Both boards are programmable array processors and are designed to facilitate the implementation of signal processing algorithms. Development tools are available for each board. For more information, contact Industrial Automation Division Marketing, (617) 329-4700.

\*SmartModel is a trademark of Logic Automation.

2–12 DSP Microprocessors

2

# ADSP-2100

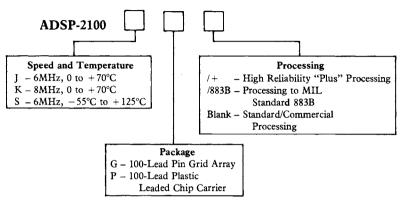

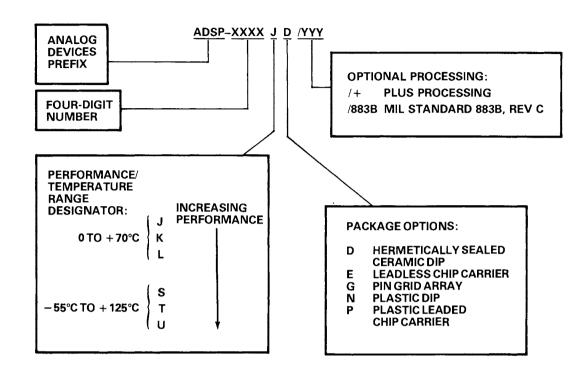

Use the following guide to select the version of the ADSP-2100 which is right for your application.

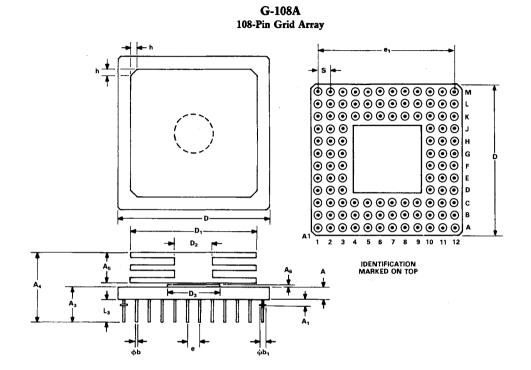

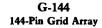

Note: Extended temperature range parts (S grade,  $-55^{\circ}$ C to  $+125^{\circ}$ C) and MIL Standard 883B parts are available only in pin grid array packages (G packages).

# Examples:

ADSP-2100KG

An 8MHz part, specified for performance at 0 to  $+70^{\circ}$ C, packaged in a 100-lead pin grid array, with standard commercial processing.

## ADSP-2100SG/883B

An 6MHz part, specified for performance at  $-55^{\circ}$ C to  $+125^{\circ}$ C, packaged in a 100-lead pin grid array, and subject to MIL Standard 883B processing.

## Ordering Cross-Software:

For a VAX - order ADDS-2110.

For a PC or compatible – order both ADDS-2121 and ADDS-2122.

For information on Cross-Software for other Operating Systems, please contact the factory.

#### Ordering an Emulator or Evaluation Board:

You will need either the ADDS-2100 or ADDS-2121 Cross-Software with your Emulator or Evaluation **B**oard. If you have already purchased one of these packages, you need not order another.

#### ADSP-2100 Development System

| Model No.  | Description                                                                                                                  | Price          |

|------------|------------------------------------------------------------------------------------------------------------------------------|----------------|

| ADDS-2110  | Cross-Software for DEC VAX/VMS<br>Computers (System Builder, Assem-<br>bler, Linker, PROM Splitter and<br>Simulator Modules) | \$2,850        |

| ADDS-2121  | Cross-Software (System Builder,<br>Assembler, Linker, PROM Splitter<br>Modules) for IBM PC and Compati-<br>bles under PC-DOS | \$ 450         |

| ADDS-2122  | Cross-Software Simulator Module<br>ONLY for IBM PC and<br>Compatibles                                                        | <b>\$</b> 975  |

| ADDS-2150  | Emulator-110V ac (Requires ADDS-<br>2110 or ADDS-2121)                                                                       | \$8,450        |

| ADDS-2150E | Emulator-220V ac (Requires ADDS-<br>2110 or ADDS-2121)                                                                       | \$8,450        |

| ADDS-2151  | Emulator-110V ac with Optional<br>Trace Board (Requires ADDS-2110<br>or ADDS-2121)                                           | *              |

| ADDS-2151E | Emulator-220V ac with Optional<br>Trace Board (Requires ADDS-2110<br>or ADDS-2121)                                           | *              |

| ADDS-2160  | Emulator Board (Requires ADDS-<br>2110 or ADDS-2121)                                                                         | *              |

| ADDS-2161  | Emulator Trace Board (Option for ADDS-2150 or ADDS-2150E)                                                                    | *              |

| ADDS-2190  | Three Day Training Course                                                                                                    | <b>\$ 9</b> 00 |

\*Available late 1987.

# **DSP Microprocessor**

# **ADSP-2100**

# FEATURES

Separate Program and Data Buses, Extended Off-Chip Single-Cycle Direct Access to 16K × 16 of Data Memory Single-Cycle Direct Access to 16K × 24 (Expandable to 32K × 24) of Program Memory **Dual Purpose Program Memory for Both Instruction** and Data Storage Three Independent Computational Units: ALU, Multiplier/Accumulator and Barrel Shifter Two Independent Data Address Generators **Powerful Program Sequencer** Internal Instruction Cache Provisions for Multiprecision Computation and **Saturation Logic** Single-Cycle Instruction Execution **Multifunction Instructions** Four External Interrupts 125ns Cycle Time 600mW Maximum Power Dissipation with CMOS Technology 100-Pin Grid Array

# APPLICATIONS

Optimized for DSP Algorithms Including Digital Filtering Fast Fourier Transforms Applications Include Image Processing Radar, Sonar Speech Processing Telecommunications

# GENERAL DESCRIPTION

The ADSP-2100 is a single-chip microprocessor optimized for digital signal processing (DSP) and other high-speed numeric processing applications. It integrates computational units, data address generators and a program sequencer in a single device.

The ADSP-2100 makes efficient use of external memories for program and data storage, freeing silicon area for increased processor performance. The resulting architecture combines the functions and performance of a bit-slice/building block system with the ease of design and development of a general-purpose microprocessor. The ADSP-2100 (K Grade) operates at 8.192MHz. Every instruction executes in a single 125ns cycle. Fabricated in a high-speed 1.5 micron double-layer metal CMOS process, the ADSP-2100 dissipates less than 600mW.

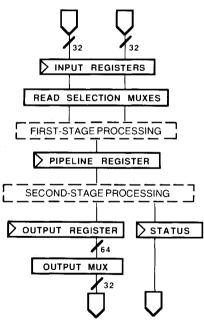

The ADSP-2100's flexible architecture and comprehensive instruction set support a high degree of operational parallelism. In one cycle the ADSP-2100 can:

- generate the next program address

- fetch the next instruction

- perform one or two data moves

- update one or two data address pointers

- perform a computational operation.

# DEVELOPMENT SYSTEM

The ADSP-2100 is supported by a complete set of tools for software and hardware system development. The Cross-Software System provides a System Builder for defining the architecture of systems under development, an Assembler, a Linker and a Simulator. The Simulator provides an interactive instruction-level simulation. A PROM Splitter generates PROM burner compatible files. An Emulator is available for hardware debugging of ADSP-2100 systems.

# **ADDITIONAL INFORMATION**

For additional information on the architecture and instruction set of the processor, refer to the ADSP-2100 User's Manual. For more information about the Development System, refer to the ADSP-2100 Cross-Software Manual and the ADSP-2100 Emulator Manual. For examples of a variety of ADSP-2100 applications routines, refer to the ADSP-2100 Applications Handbook, Volume 1. Manuals are available from your local Analog Devices sales office. See ordering information.

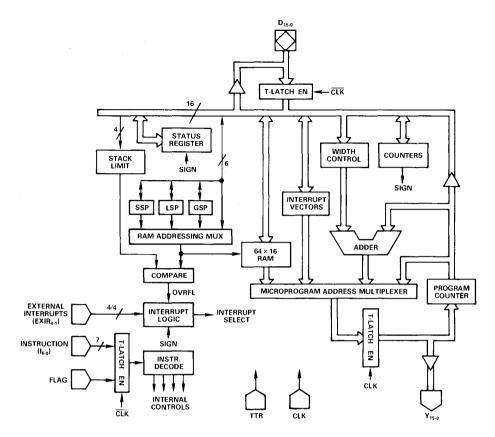

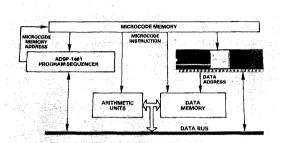

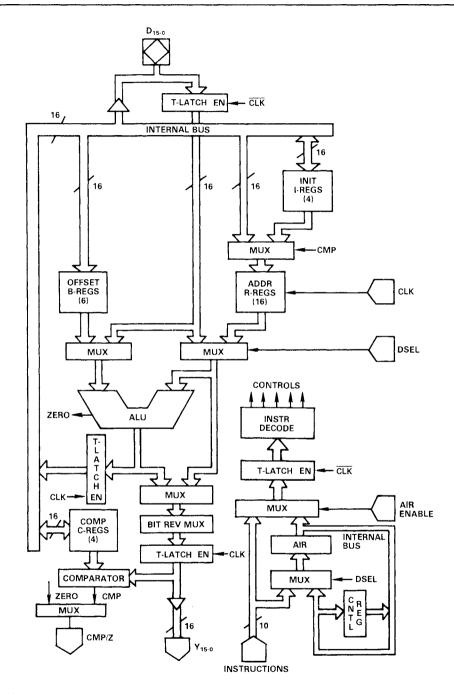

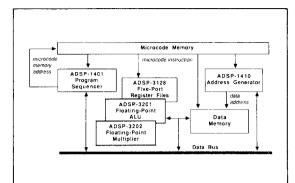

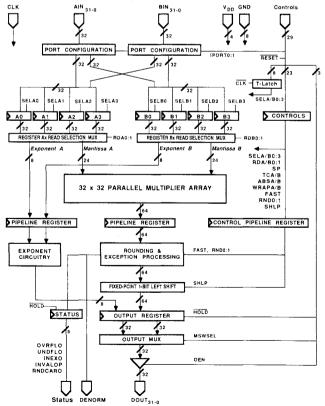

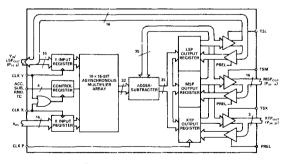

## ARCHITECTURE OVERVIEW

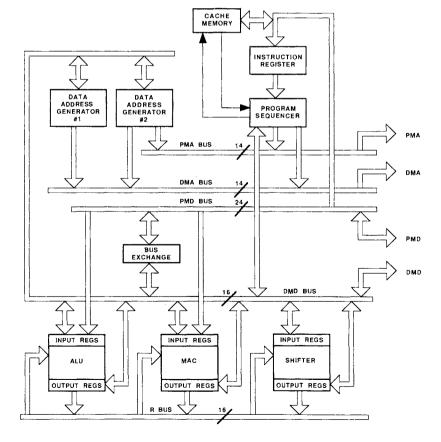

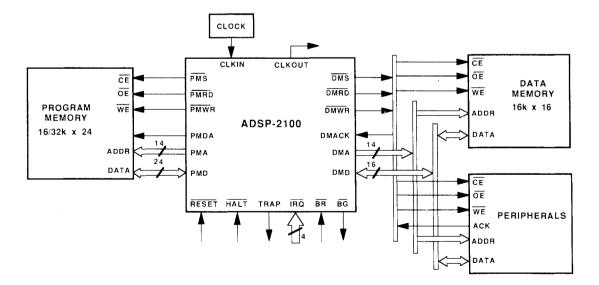

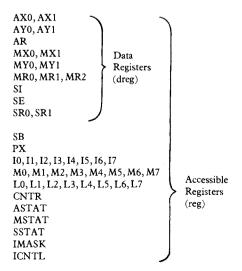

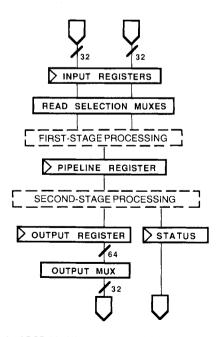

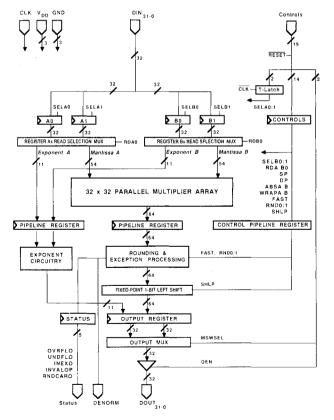

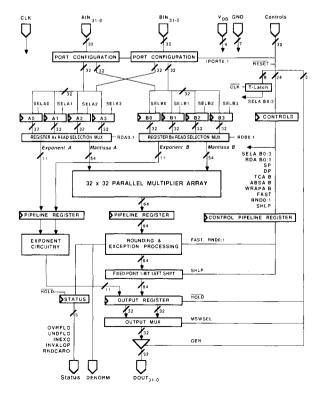

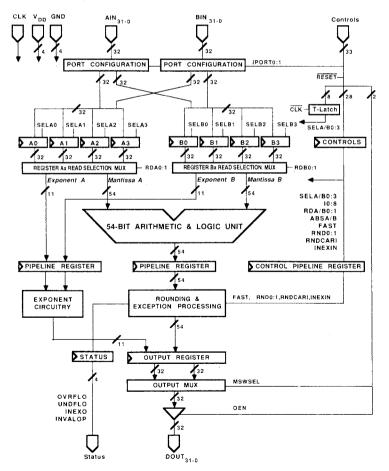

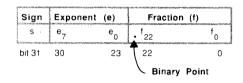

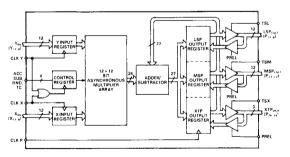

Figure 1 is an overall block diagram of the ADSP-2100. The processor contains three independent computational units: the ALU, the multiplier/accumulator (MAC) and the Shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add and multiply/subtract operations. The Shifter performs logical and arithmetic shifts, normalization, denormalization and derive exponent operations. The Shifter can be used to efficiently implement any degree of numeric format control, up to and including full floating point representations. The computational units are arranged side-by-side instead of serially for flexible operation sequencing. The internal result (R) bus directly connects the computational units so that the output of any unit may be the input of any unit on the next cycle.

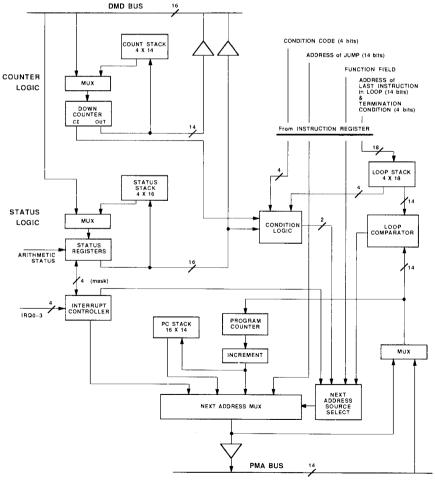

A powerful program sequencer and two dedicated data address generators ensure efficient use of these computational units. The program sequencer generates the next instruction address. To minimize overhead cycles, the sequencer supports conditional jumps, subroutine calls and returns in a single cycle. With internal loop counters and loop stacks, the ADSP-2100 executes looped code with zero overhead; no explicit jump instructions are required to maintain the loop.

The data address generators (DAGs) handle address pointer updates. Each DAG keeps track of up to four address pointers.

Whenever the pointer is used to access external data (indirect addressing), it is modified by a prespecified value. A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers. With two independent DAGs, the processor can generate two addresses simultaneously for dual operand fetches.

Efficient data transfer is achieved with the use of five internal buses.

- Program Memory Address (PMA) bus

- Program Memory Data (PMD) bus

- Data Memory Address (DMA) bus

- Data Memory Data (DMD) bus

- Result (R) bus

The program memory (PMD, PMA) buses and data memory (DMA, DMD) buses extend off-chip to provide direct connections to external memories. The DMD bus is the primary bus for routing data internally and to/from external data memory. The 14-bit DMA bus provides direct addressing of  $16K \times 16$  of external memory. Although the primary function of the program memory is for storing instructions, it can also store data. In this case, the PMD bus provides a path for routing data to/from program memory, permitting dual operand fetches. The 14-bit PMA bus provides direct addressing to  $16K \times 24$  of external memory, expandable to  $32K \times 24$  by using the program memory data access (PMDA) signal as the 15th address line.

Figure 1. ADSP-2100 Block Diagram

When a data fetch from program memory is required, an extra memory cycle is automatically appended to enable the next instruction fetch. To avoid this extra cycle, the ADSP-2100 has an internal instruction cache (16 instructions deep) which serves as an alternate source for the next instruction. The cache monitor circuit transparently determines when the cache contents are valid. When the next instruction is in the cache, no extra cycle is necessary.

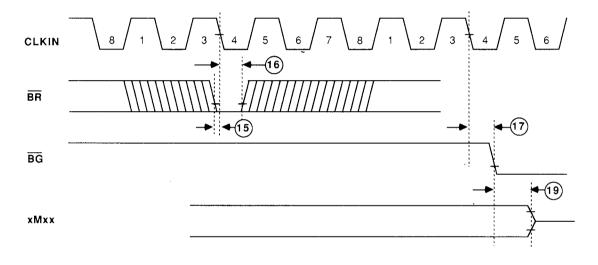

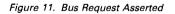

The data memory interface supports slower memories and memorymapped peripherals with wait states. The data memory acknowledge (DMACK) signal provides the necessary handshake. External devices can gain control of program or data buses independently with bus request/ grant signals ( $\overline{BR}$ , and  $\overline{BG}$ ). The ADSP-2100 can respond to four external interrupts, which are internally prioritized, maskable and independently programmable as either edge- or level-sensitive. Additional external controls are provided by the RESET, HALT, and TRAP signals. With both BR and RESET recognized, the ADSP-2100 idles, consuming the least possible current.

The ADSP-2100 instruction set provides flexible data moves and multifunction (data moves with a computation) instructions. Every instruction can be executed in a single processor cycle. The ADSP-2100 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

A pin description and detailed discussion of each section of the ADSP-2100 follows.

#### **Pin Description**

This section summarizes the pin description of the processor by interface. In this data sheet, when groups of pins are identified with subscripts, as in  $PMD_{23-0}$ , the highest numbered pin  $(PMD_{23})$  is the MSB.

| Pin Name               | Туре         | Function                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks:                |              |                                                                                                                                                                                                                                                                                                                                                                                            |

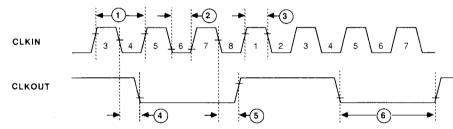

| CLKIN                  | Input        | Master input clock operating at four times the processor instruction rate. Nominally 50% duty cycle. The phases of CLKIN define the eight internal processor states making up one instruction cycle. J and S grades operate at 6.144MHz and K grade operates at 8.192MHz. CLKIN must be four times these frequencies.                                                                      |

| CLKOUT                 | Output       | Output clock operating at the processor instruction rate with a 50% duty cycle. Synchronized to the internal processor states.                                                                                                                                                                                                                                                             |

| Interrupt Rec          | juest Lines: |                                                                                                                                                                                                                                                                                                                                                                                            |

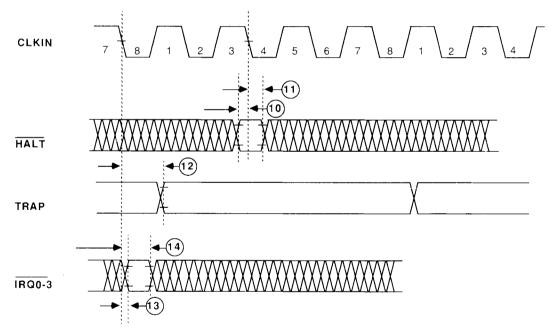

| $\overline{IRQ}_{3-0}$ | Input        | Interrupt Request lines that may be either edge triggered or level sensitive. Interrupts are prioritized and individually maskable.                                                                                                                                                                                                                                                        |

| Control Inter          | face:        |                                                                                                                                                                                                                                                                                                                                                                                            |

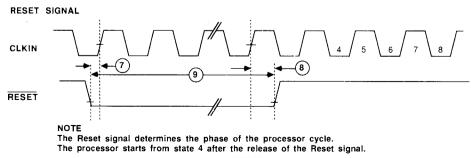

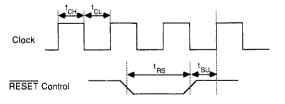

| RESET                  | lnput        | Master Reset must be asserted long enough to assure proper reset. When $\overline{\text{RESET}}$ is released, execution begins at program memory location 0004.                                                                                                                                                                                                                            |

| HALT                   | Input        | Used to halt the processor. All control signals become inactive and the address and data buses are driven for observation.                                                                                                                                                                                                                                                                 |

| TRAP                   | Output       | Used to indicate the execution of a TRAP instruction. Remains asserted until $\overline{HALT}$ is asserted by an external device.                                                                                                                                                                                                                                                          |

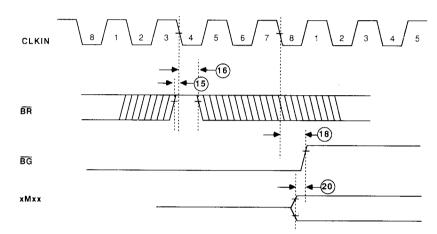

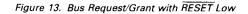

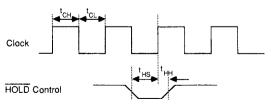

| BR                     | Input        | Bus Request used by an external device to request control of the program and data memory interface.<br>Upon receiving BR the processor halts execution at the completion of the current cycle and relinquishes<br>the program and data memory interface by tristating PMA, PMD, PMS, PMWR, PMRD, PMDA,<br>DMA, DMD, DMS, DMRD and DMWR. The processor regains control when BR is released. |

| BG                     | Output       | Bus Grant. Acknowledges a bus request $(\overline{BR})$ , indicating that the external device may take control.<br>BG is held asserted until $\overline{BR}$ is released.                                                                                                                                                                                                                  |

|                        |              |                                                                                                                                                                                                                                                                                                                                                                                            |

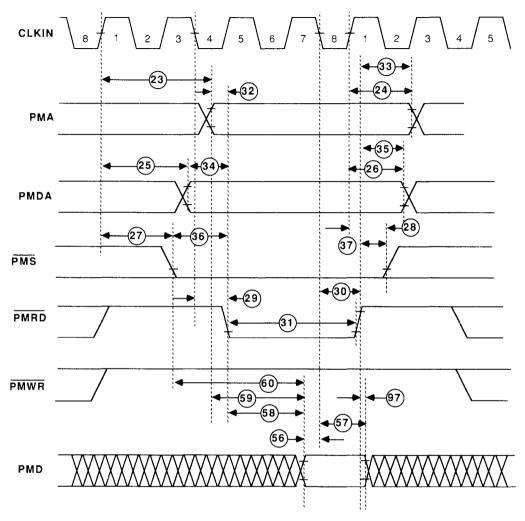

# **Program Memory Interface:**

| PMA <sub>13-0</sub> | Output        | Program Memory Address Bus; tristated when $\overline{BG}$ is asserted.                                                                                                           |

|---------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMD <sub>23-0</sub> | Bidirectional | Program Memory Data Bus; tristated when $\overline{BG}$ is asserted.                                                                                                              |

| PMS                 | Output        | Program Memory Select signals a program memory access on the PM interface. Also usable as a chip select signal for external memories. Tristated when $\overline{BG}$ is asserted. |

| PMRD                | Output        | Program Memory Read indicates a read operation on the PM interface. Also usable as a read strobe or output enable signal. Tristated when $\overline{BG}$ is asserted.             |

| PMWR                | Output        | Program Memory Write establishes the direction of data transfer on the PM interface. Also usable as a write strobe. Tristated when $\overline{BG}$ is asserted.                   |

PMDA

Output

Program Memory Data Access used to distinguish instruction and data fetches from PM. Asserted high when data, as opposed to instruction, is accessed. Also usable as a fifteenth PM address bit. Tristated when BG is asserted.

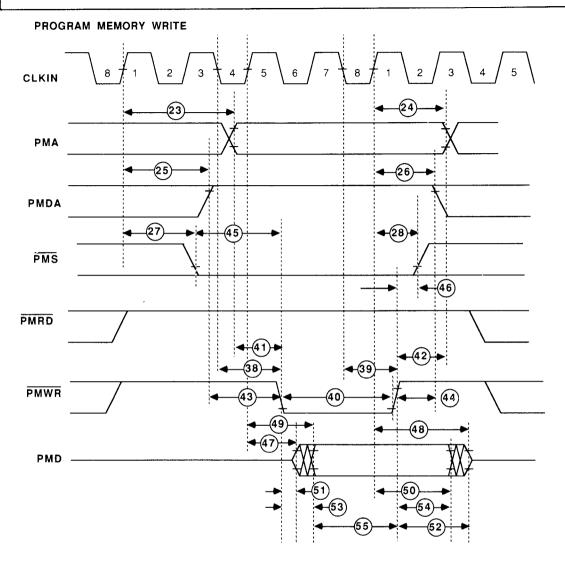

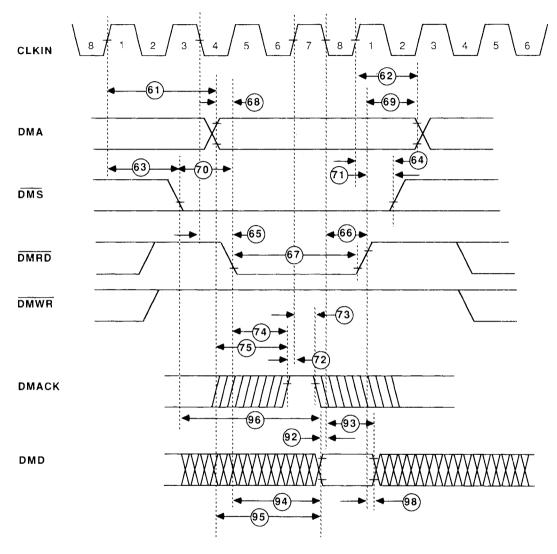

#### **Data Memory Interface:**

| DMA <sub>13-0</sub> | Output        | Data Memory Address Bus; tristated when $\overline{BG}$ is asserted.                                                                                                                                                                                                                                  |

|---------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $DMD_{15-0}$        | Bidirectional | Data Memory Data Bus; tristated when $\overline{BG}$ is asserted.                                                                                                                                                                                                                                     |

| DMS                 | Output        | Data Memory Select signals the a Data Memory Access on the Data Memory interface. Also usable as a chip select signal for external memories. Tristated when $\overline{BG}$ is asserted.                                                                                                              |

| DMRD                | Output        | Data Memory Read indicates a read operation on the Data Memory interface. Also usable as a read strobe or output enable signal. Tristated when $\overline{BG}$ is asserted.                                                                                                                           |

| DMWR                | Output        | Data Memory Write indicates a write operation on the Data Memory interface. Also usable as a write strobe. Tristated when $\overline{BG}$ is asserted.                                                                                                                                                |

| DMACK               | Input         | Data Memory Acknowledge signal used for asynchronous transfers across the DM interface. Indicates that data memory or memory-mapped peripherals are ready for data transfer. If DMACK is not asserted when checked by the processor, wait states are automatically generated until DMACK is asserted. |

| Supply Rails:       |               | · · ·                                                                                                                                                                                                                                                                                                 |

| $V_{DD}$            | Supply        | Power supply rail nominally $+5$ VDC. There are four $V_{DD}$ pins.                                                                                                                                                                                                                                   |

| ONTE                | <u> </u>      |                                                                                                                                                                                                                                                                                                       |

GND Ground Power supply return. There are nine GND pins.

### Arithmetic/Logic Unit

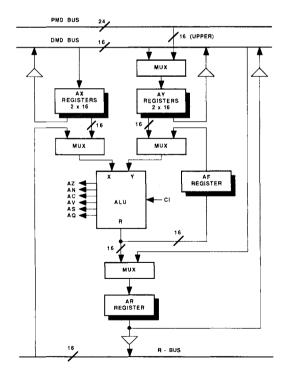

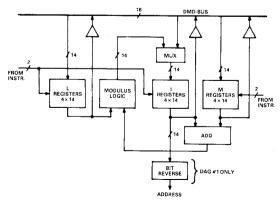

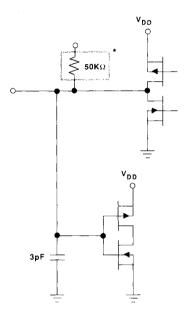

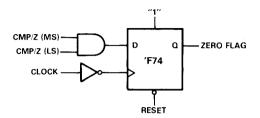

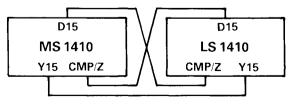

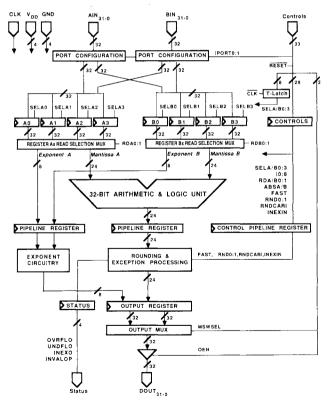

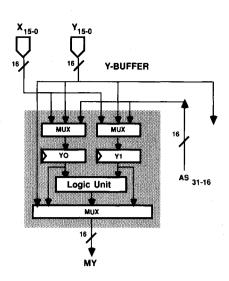

Figure 2 shows a block diagram of the Arithmetic/Logic Unit (ALU).

Figure 2. ALU Block Diagram

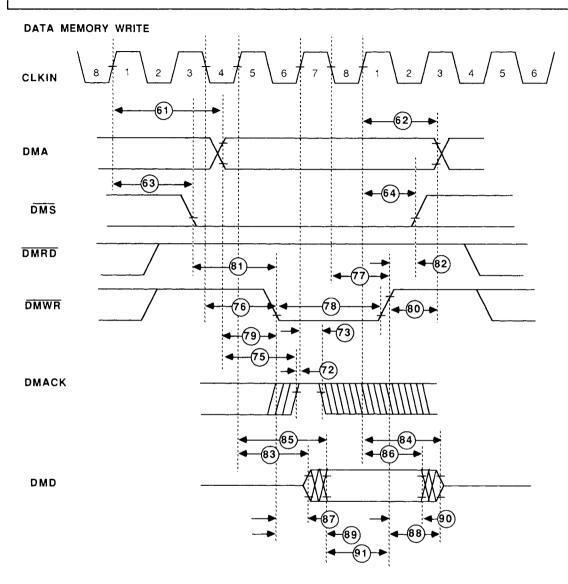

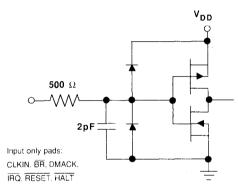

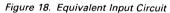

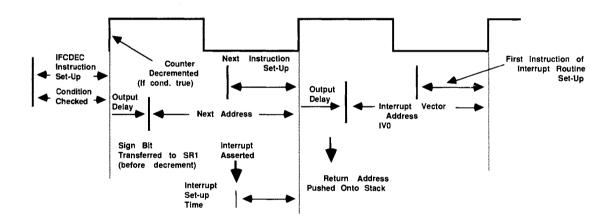

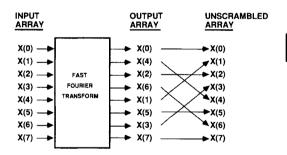

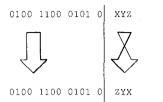

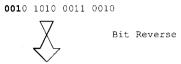

The ALU provides a standard set of general purpose arithmetic and logic functions: add, subtract, negate, increment, decrement, absolute value, AND, OR, Exclusive OR and NOT. Two divide primitives are also provided to facilitate division. The ALU takes two 16-bit inputs, X and Y, and generates one 16-bit output, R. It accepts the carry (AC) bit in the arithmetic status register (ASTAT) as the carry-in (CI) bit. The carry-in feature enables multiprecision computations. Six arithmetic status bits are generated: AZ (zero), AN (negative), AV (overflow), AC (carry), AS (sign) and AQ (quotient). These status bits are latched in ASTAT.