MC68881UM/AD REV 1

## MC68881/MC68882 Floating-Point Coprocessor User's Manual

# MC68881/MC68882 THE FLOATING-POINT PERFORMANCE STANDARD

MOTOROLA

| General Description                      | 1  |

|------------------------------------------|----|

| Programming Model                        | 2  |

| <b>Operand Data Formats</b>              | 3  |

| Instruction Set                          | 4  |

| Coprocessor Programming                  | 5  |

| Exception Processing                     | 6  |

| Coprocessor Interface                    | 7  |

| Instruction Execution Timing             | 8  |

| Functional Signal Descriptions           | 9  |

| Bus Operation                            | 10 |

| Interfacing Methods                      | 11 |

| Electrical Specifications                | 12 |

| Ordering Information and Mechanical Data | 13 |

| Glossary                                 | Α  |

| Abbreviations and Acronyms               | В  |

| Index                                    |    |

## MC68881/MC68882

## FLOATING-POINT COPROCESSOR USER'S MANUAL

**First Edition**

PRENTICE HALL, Englewood Cliffs, N.J. 07632

This document contains information on a new product. Specifications and information herein are subject to change without notice. Motorola reserves the right to make changes to any products herein to improve functioning or design. Although the information in this document has been carefully reviewed and is believed to be reliable, Motorola does not assume any liabiliy arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of other.

Motorola, Inc. general policy does not recommend the use of its components in life support applications where in a failure or malfunction of the component may directly threaten life or injury. Per Motorola Terms and Conditions of Sale, the user of Motorola components in life support applications assumes all risk of such use and indemnifies Motorola against all damages.

### PREFACE

This manual assumes that the MC68881/MC68882 is connected as a coprocessor to the MC68020/MC68030 microprocessor. If the MC68881/MC68882 is used in a system with a main processor other than the MC68020/MC68030, it is expected that the main processor emulates the M68000 Family coprocessor interface as required by the MC68881/MC68882.

This manual is divided into two major parts. The first part, sections 2 through 8, describes the programmer's model of the MC68881/MC68882 and the floating-point instruction set that it implements. This part of the manual includes a detailed description of each instruction and a section on instruction timing that can be used for program optimization and to predict floating-point arithmetic performance.

The second part of the manual, sections 9 through 13, describes the hardware interface of the MC68881/MC68882 to the main processor, and is most pertinent to system hardware designers. Bus cycle timing diagrams, interface register addressing, etc., are discussed from the viewpoint of the MC68020/MC68030 hardware conventions. A prior knowledge of the MC68020/MC68030 bus interface, particularly as it pertains to the M68000 Family coprocessor interface, is quite helpful in understanding the operation of the MC68881/MC68882 bus interface.

Throughout this manual, M68000 or M68000 Family is used to refer to the family of devices that support the Motorola 68000 Family architecture. A number that is preceded by MC, such as MC68020, MC68030, MC68881, or MC68882, refers to a specific part. A reference to MC68881/MC68882 or FPCP applies to either floating-point coprocessor, and a reference to MC68020/MC68030 or MPU applies to either main processor.

The sections and appendices of the manual are:

- Section 1. General Description

- Section 2. Programming Model

- Section 3. Operand Data Formats

- Section 4. Instruction Set

- Section 5. Coprocessor Programming

- Section 6. Exception Processing

- Section 7. Coprocessor Interface

- Section 8. Instruction Execution Timing

- Section 9. Functional Signal Descriptions

- Section 10. Bus Operation

- Section 11. Interfacing Methods

- Section 12. Electrical Specifications

- Section 13. Ordering Information and Mechanical Data

Appendix A. Glossary

Appendix B. Abbreviations and Acronyms

## TABLE OF CONTENTS

#### Paragraph Number

#### Title

#### Page Number

#### Section 1 General Description

| 1.1   | The Coprocessor Concept                | 1-2  |

|-------|----------------------------------------|------|

| 1-2   | Hardware Overview                      | 1-2  |

| 1.2.1 | Bus Interface Unit                     | 1-6  |

| 1.2.2 | Coprocessor Interface                  | 1-8  |

| 1.3   | Operand Data Formats                   | 1-9  |

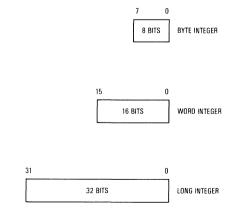

| 1.3.1 | Integer Data Formats                   | 1-9  |

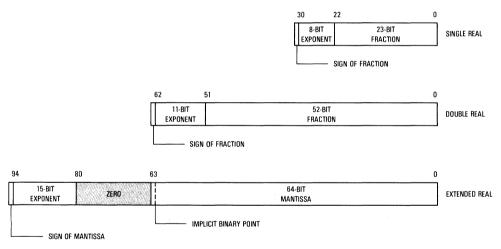

| 1.3.2 | Floating-Point Data Formats            | 1-9  |

| 1.3.3 | Packed Decimal String Real Data Format | 1-10 |

| 1.3.4 | Data Format Summary                    | 1-10 |

| 1.4   | Instruction Set                        | 1-12 |

| 1.4.1 | Moves                                  | 1-12 |

| 1.4.2 | Move Multiple Registers                | 1-12 |

| 1.4.3 | Monadic Operations                     | 1-13 |

| 1.4.4 | Dyadic Operations                      | 1-13 |

| 1.4.5 | Branch, Set, and Trap-On Condition     | 1-13 |

| 1.4.6 | Miscellaneous Instructions             | 1-14 |

| 1.5   | Addressing Modes                       | 1-14 |

| 1.6   | MC68882 Programming Considerations     | 1-14 |

## Section 2

#### **Programming Model**

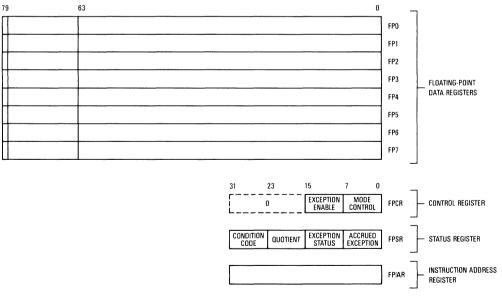

| 2.1   | Floating-Point Data Registers               | 2-1 |

|-------|---------------------------------------------|-----|

| 2.2   | Floating-Point Control Register             | 2-2 |

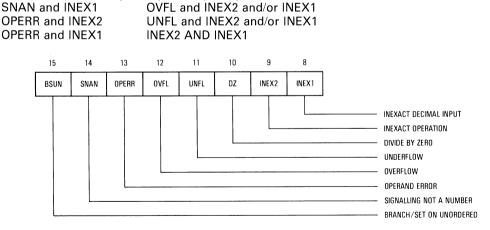

| 2.2.1 | FPCR Exception Enable Byte                  | 2-2 |

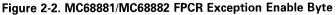

| 2.2.2 | FPCR Mode Control Byte                      | 2-3 |

| 2.3   | Floating-Point Status Register              | 2-4 |

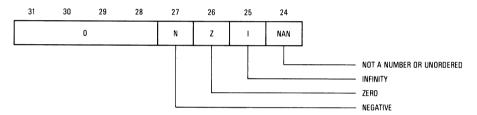

| 2.3.1 | FPSR Floating-Point Condition Code Byte     | 2-4 |

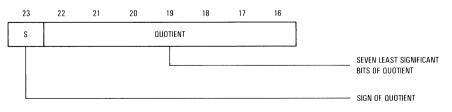

| 2.3.2 | FPSR Quotient Byte                          | 2-5 |

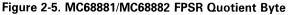

| 2.3.3 | FPSR Exception Status Byte                  | 2-6 |

| 2.3.4 | FPSR Accrued Exception Byte                 | 2-6 |

| 2.4   | Floating-Point Instruction Address Register | 2-7 |

#### Section 3 Operand Data Formats

| 3.1   | Integer Data Formats     | 3-1 |

|-------|--------------------------|-----|

| 3.2   | Binary Real Data Formats | 3-2 |

| 3.2.1 | Normalized Numbers       | 3-4 |

| 3.2.2 | Denormalized Numbers     | 3-4 |

| 3.2.3 | Zeros                    | 3-5 |

| Paragraph<br>Number | Title                                        | Page<br>Numbe |

|---------------------|----------------------------------------------|---------------|

| 3.2.4               | Infinities                                   | . 3-5         |

| 3.2.5               | Not-A-Numbers                                | . 3-5         |

| 3.2.6               | Binary Real Data Summary                     | . 3-6         |

| 3.3                 | Packed Decimal Real Data Format              | . 3-6         |

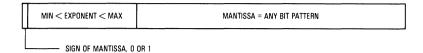

| 3.4                 | Internal Data Format                         | . 3-7         |

| 3.5                 | Format Conversions                           | . 3-8         |

| 3.5.1               | Conversion to Extended Precision Data Format | . 3-8         |

| 3.5.2               | Conversions to Other Data Formats            | . 3-8         |

| 3.6                 | Data Format Details                          | . 3-8         |

#### Section 4

#### **Instruction Set**

| 4.1     | Instruction Description Conventions                        |       |

|---------|------------------------------------------------------------|-------|

| 4.2     | Instruction Groups                                         |       |

| 4.2.1   | Data Movement Operations                                   | 4-2   |

| 4.2.2   | Dyadic Operations                                          |       |

| 4.2.3   | Monadic Operations                                         | 4-3   |

| 4.2.4   | Program Control Operations                                 | 4-4   |

| 4.2.5   | System Control Operations                                  | 4-5   |

| 4.3     | Computational Accuracy                                     | 4-5   |

| 4.3.1   | Arithmetic Instructions                                    | 4-6   |

| 4.3.2   | Transcendental Instructions                                | 4-7   |

| 4.3.3   | Decimal Conversions                                        | 4-7   |

| 4.4     | Conditional Test Definitions                               | 4-8   |

| 4.4.1   | IEEE Non-Aware Tests                                       | 4-9   |

| 4.4.2   | IEEE Aware Tests                                           | 4-10  |

| 4.4.3   | Miscellaneous Tests                                        | 4-10  |

| 4.5     | Detailed Instruction Descriptions                          | 4-10  |

| 4.5.1   | Addressing Modes                                           | 4-10  |

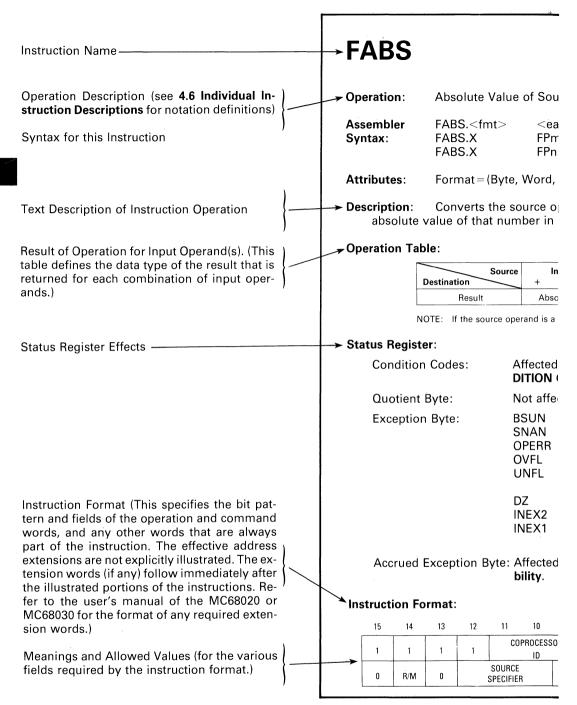

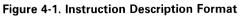

| 4.5.2   | Instruction Description Format                             | 4-11  |

| 4.5.3   | Operation Tables                                           | 4-13  |

| 4.5.4   | NANs                                                       | 4-13  |

| 4.5.4.1 | Non-Signaling NANs                                         |       |

| 4.5.4.2 | Signaling NANs                                             | 4-13  |

| 4.5.5   | Operation Post Processing                                  |       |

| 4.5.5.1 | Setting Floating-Point Condition Codes                     | 4-14  |

| 4.5.5.2 | Underflow, Round, Overflow                                 | 4-14  |

| 4.6     | Individual Instruction Descriptions                        | 4-15  |

| 4.7     | Instruction Encoding Details                               | 4-120 |

| 4.7.1   | General Type Coprocessor Instruction Format                | 4-120 |

| 4.7.1.1 | Register-to-Register Instructions                          | 4-121 |

| 4.7.1.2 | External Operand-to-Register Instructions                  | 4-122 |

| 4.7.1.3 | Move Constant to Floating-Point Data Register Instructions | 4-123 |

| 4.7.1.4 | Move to External Destination Instructions                  |       |

| 4.7.1.5 | Move System Control Register Instructions                  | 4-125 |

| 4.7.1.6 | Move Multiple Floating-Point Data Registers Instructions   |       |

| 4.7.1.7 | Undefined, Reserved Command Words                          |       |

e

#### Paragraph Number

#### Title

#### Page Number

#### Section 5 Coprocessor Programming

|         | coprocessor rrogramming                                         |      |

|---------|-----------------------------------------------------------------|------|

| 5.1     | Applications Programming                                        | 5-1  |

| 5.1.1   | Concurrency                                                     | 5-1  |

| 5.1.1.1 | Concurrent Integer and Floating-Point Computations              | 5-1  |

| 5.1.1.2 | Concurrent Floating-Point Computations                          | 5-2  |

| 5.1.2   | Optimization of Code for the MC68882                            | 5-8  |

| 5.1.2.1 | Unrolling Loops                                                 | 5-8  |

| 5.1.2.2 | Avoiding Register Conflicts                                     | 5-8  |

| 5.1.2.3 | Arranging FMOVE Instructions                                    | 5-8  |

| 5.1.2.4 | Performance Improvement Example                                 | 5-9  |

| 5.2     | Systems Programming                                             | 5-9  |

| 5.2.1   | State Frame Sizes                                               | 5-9  |

| 5.2.2   | Exception Handler Code                                          | 5-10 |

| 5.2.3   | Processing of Special Conditions                                | 5-12 |

| 5.2.3.1 | Interrupts                                                      | 5-12 |

| 5.2.3.2 | Bus Arbitration                                                 | 5-12 |

| 5.2.3.3 | Context Switching                                               | 5-12 |

| 5.2.3.4 | Bus Errors                                                      | 5-13 |

| 5.2.3.5 | Exception Processing                                            | 5-13 |

| 5.2.3.6 | Simultaneous Floating-Point Exception and Task Switch Interrupt | 5-13 |

| 5.2.4   | Detecting Coprocessor Presence                                  | 5-14 |

|         |                                                                 |      |

#### Section 6 Exception Processing

| 6.1   | Coprocessor-Detected Exceptions | 6-2  |

|-------|---------------------------------|------|

| 6.1.1 | Branch/Set on Unordered (BSUN)  | 6-5  |

| 6.1.2 | Signaling Not-a-Number          | 6-6  |

| 6.1.3 | Operand Error                   | 6-7  |

| 6.1.4 | Overflow                        | 6-9  |

| 6.1.5 | Underflow                       | 6-10 |

| 6.1.6 | Divide by Zero                  | 6-13 |

|       |                                 |      |

#### Paragraph Page Number Title Number 6.1.7 6.1.8 6.1.9 6.1.10 6.1.11 6.1.12 6.1.13 6.2 6.2.1 6.2.2 6.2.3 6.2.4 6.2.5 6.2.6 6.2.7 6.2.8 6.3 6.4 6.4.1 6.4.2 State Frames 6-28 6.4.2.1 6.4.2.2 6.4.2.3 6.4.3 6.4.3.1 Reset Phase 6-36 6.4.3.2 6.4.3.3 6.4.3.4 6.4.3.5 6.4.4 FRESTORE Protocol 6-37 6.4.5

#### Section 7

#### **Coprocessor Interface**

| 7.1    | Chip-Select Decode              | 7-1 |

|--------|---------------------------------|-----|

| 7.2    | Coprocessor Interface Registers | 7-2 |

| 7.2.1  | Response CIR (\$00)             | 7-3 |

| 7.2.2  | Control CIR (\$02)              | 7-3 |

| 7.2.3  | Save CIR (\$04)                 | 7-4 |

| 7.2.4  | Restore CIR (\$06)              | 7-5 |

| 7.2.5  | Operation Word CIR (\$08)       | 7-5 |

| 7.2.6  | Command CIR (\$0A)              | 7-5 |

| 7.2.7  | Condition CIR (\$0E)            | 7-5 |

| 7.2.8  | Operand CIR (\$10)              | 7-6 |

| 7.2.9  | Register Select CIR (\$14)      | 7-6 |

| 7.2.10 | Instruction Address CIR (\$18)  |     |

| 7.2.11 | Operand Address CIR (\$1C)      |     |

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

| 7.3                 | Interprocessor Transfers                               | . 7-8          |

| 7.4                 | Coprocessor Instructions                               |                |

| 7.4.1               | Instruction Protocol.                                  |                |

| 7.4.2               | Response Primitives                                    |                |

| 7.4.2.1             | Null Primitive                                         |                |

| 7.4.2.2             | Evaluate Effective Address and Transfer Data Primitive |                |

| 7.4.2.3             | Transfer Single Main Processor Register Primitive      | . 7-13         |

| 7.4.2.4             | Transfer Multiple Coprocessor Registers Primitive      |                |

| 7.4.2.5             | Take Pre-Instruction Exception Primitive               |                |

| 7.4.2.6             | Take Mid-Instruction Exception Primitive               |                |

| 7.4.2.7             | Response Primitive Summary                             | 7-17           |

| 7.5                 | Instruction Dialogs                                    |                |

| 7.5.1               | General Instructions                                   | . 7-20         |

| 7.5.1.1             | Register-to-Register (OPCLASS 000)                     |                |

| 7.5.1.2             | External-to-Register (OPCLASS 010)                     | 7-21           |

| 7.5.1.3             | Register-to-External (OPCLASS 011)                     | 7-22           |

| 7.5.1.4             | Move Control Registers (OPCLASS 100 and 101)           | . 7-24         |

| 7.5.1.5             | Move Multiple FPn (OPCLASS 110 and 111)                |                |

| 7.5.2               | Conditional Instructions                               | 7-26           |

| 7.5.3               | Context Switch Instructions                            | 7-26           |

| 7.5.3.1             | FSAVE                                                  |                |

| 7.5.3.2             | FRESTORE                                               |                |

| 7.5.4               | Exception Processing                                   |                |

| 7.5.4.1             | Take Pre-Instruction Exception                         |                |

| 7.5.4.2             | Take Mid-Instruction Exception                         |                |

| 7.5.4.3             | Mid-Instruction Interrupt                              |                |

| 7.5.4.4             | Take BSUN Exception                                    |                |

| 7.5.4.5             | F-Line Emulator Exception                              |                |

| 7.5.4.6             | Format Exception, FSAVE Instruction                    |                |

| 7.5.4.7             | Format Exception, FRESTORE Instruction                 | 7-38           |

## Section 8

| 8.1     | Factors Affecting Execution Times           | 8-1  |

|---------|---------------------------------------------|------|

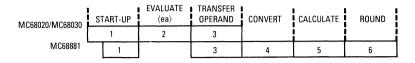

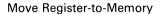

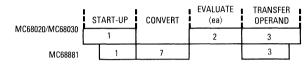

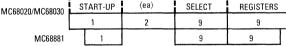

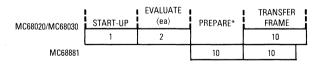

| 8.1.1   | Instruction Start-Up Phase                  | 8-2  |

| 8.1.2   | Calculation Phase                           | 8-3  |

| 8.1.3   | Round/Store Result Phase                    | 8-3  |

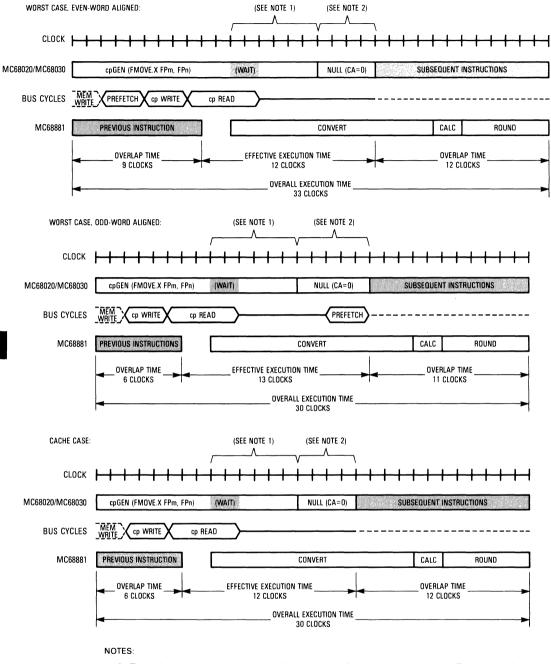

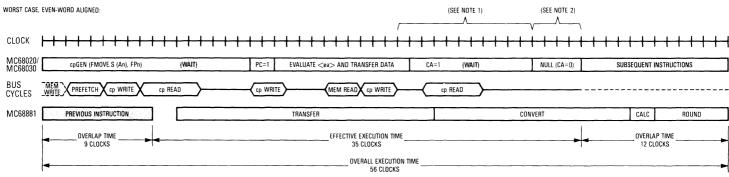

| 8.2     | Concurrent Instruction Execution            | 8-4  |

| 8.3     | Interrupt Latency Times                     | 8-5  |

| 8.4     | Coprocessor Interface Overhead              | 8-6  |

| 8.5     | Execution Timing Tables                     | 8-8  |

| 8.5.1   | Timing Tables for Typical Execution         | 8-10 |

| 8.5.1.1 | Effective Address Calculations              | 8-10 |

| 8.5.1.2 | Arithmetic Operations                       | 8-11 |

| 8.5.1.3 | MC68882 Concurrent Operations               | 8-14 |

| 8.5.1.4 | Move Control Register and FMOVEM Operations | 8-15 |

|         |                                             |      |

#### Paragraph Number

#### Title

#### Page Number

| 8.5.1.5<br>8.5.1.6<br>8.5.2<br>8.5.2.1<br>8.5.2.2<br>8.5.2.3<br>8.5.2.3<br>8.5.2.4<br>8.5.2.5<br>8.5.2.5<br>8.5.2.6<br>8.5.2.7<br>8.5.2.8<br>8.5.2.9<br>8.5.2.9<br>8.5.2.10 | Conditional Instructions<br>FSAVE and FRESTORE Instructions<br>MC68881 Detail Timing Tables<br>Instruction Start-Up<br>Transfer Operand<br>Input Operand Conversion<br>Arithmetic Calculation<br>Output Operand Conversion<br>Rounding and Exception Handling<br>Conditional Termination<br>Multiple Register Transfer<br>State Frame Transfer | 8-17<br>8-23<br>8-24<br>8-25<br>8-27<br>8-30<br>8-31<br>8-32<br>8-34<br>8-34 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 8.5.2.9<br>8.5.2.10<br>8.6                                                                                                                                                  | Exception Processing<br>Main Processor Instruction Overlap Timing                                                                                                                                                                                                                                                                              | 8-35                                                                         |

|                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                |                                                                              |

#### Section 9 **Functional Signal Descriptions**

| 9.1  | Address Bus (A0 through A4)                         | 9-1 |

|------|-----------------------------------------------------|-----|

| 9.2  | Data Bus (D0 through D31)                           | 9-2 |

| 9.3  | Size (SIZE)                                         | 9-2 |

| 9.4  | Address Strobe (AS)                                 | 9-2 |

| 9.5  | Chip Select (CS)                                    | 9-3 |

| 9.6  | Read/Write (R/₩)                                    | 9-3 |

| 9.7  | Data Strobe (DS)                                    | 9-3 |

| 9.8  | Data Transfer and Size Acknowledge (DSACK0, DSACK1) | 9-3 |

| 9.9  | Reset (RESET)                                       | 9-4 |

| 9.10 | Clock (CLK)                                         | 9-4 |

| 9.11 | Sense Device (SENSE)                                | 9-4 |

| 9.12 | Power (V <sub>CC</sub> and GND)                     | 9-4 |

| 9.13 | No Connect (NC)                                     | 9-6 |

| 9.14 | Signal Summary                                      | 9-6 |

|      |                                                     |     |

### Section 10

#### **Bus Operation** Basic Transfer Mechanism Overview...... 10-1 32-Bit Port Size ..... Reset Operation...... 10-5 Chip Select Timing ...... 10-6

10.1

10.1.1

10.1.2

10.1.3 10.2

10-2

## **TABLE OF CONTENTS (Concluded)**

| Paragraph<br>Number | Title                                       | Page<br>Number |

|---------------------|---------------------------------------------|----------------|

| 10.5                | Inter-Cycle Timing Restrictions             | 10-12          |

| 10.6                | Coprocessor Interface Protocol Restrictions | 10-14          |

#### Section 11 Interfacing Methods

| 11.1   | FPCP and MPU Interfacing                        | 11-1 |

|--------|-------------------------------------------------|------|

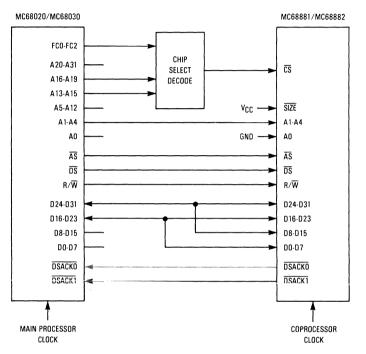

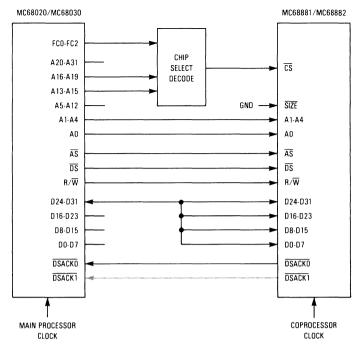

| 11.1.1 | 32-Bit Data Bus Coprocessor Connection          |      |

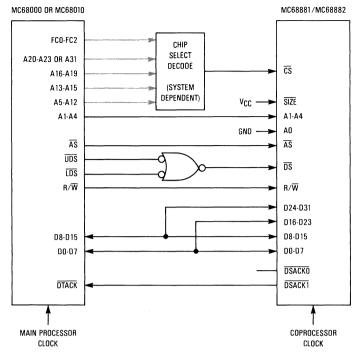

| 11.1.2 | 16-Bit Data Bus Coprocessor Connection          |      |

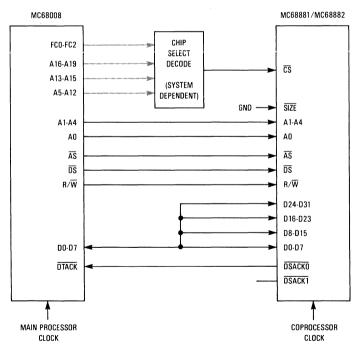

| 11.1.3 | 8-Bit Data Bus Coprocessor Connection           |      |

| 11.2   | Interfacing the FPCP as a Peripheral            | 11-2 |

| 11.2.1 | 16-Bit Data Bus Peripheral Processor Connection |      |

| 11.2.2 | 8-Bit Data Bus Peripheral Processor Connection  | 11-3 |

| 11.3   | Peripheral Processor Operation                  |      |

|        |                                                 |      |

#### Section 12 Electrical Specifications

| 12.1 | Maximum Ratings                                       | 12-1 |

|------|-------------------------------------------------------|------|

| 12.2 | Thermal Characteristics — PGA Package                 |      |

| 12.3 | Power Considerations                                  |      |

| 12.4 | DC Electrical Characteristics                         | 12-2 |

| 12.5 | AC Electrical Characteristics — Clock Input           | 12-3 |

| 12.6 | AC Electrical Characteristics — Read and Write Cycles | 12-4 |

#### Section 13

#### **Ordering Information and Mechanical Data**

| 13.1 | Standard MC68881/MC68882 Order Information | 13-1 |

|------|--------------------------------------------|------|

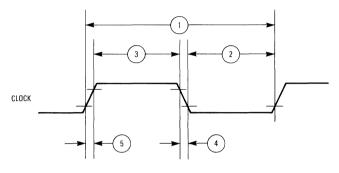

| 13.2 | Pin Assignments                            | 13-2 |

| 13.3 | Package Dimensions                         | 13-3 |

#### Appendix A Glossary

#### Appendix B Abbreviations and Acronyms

#### Index

## LIST OF ILLUSTRATIONS

| Figure<br>Number | Title                                                           | Page<br>Number |

|------------------|-----------------------------------------------------------------|----------------|

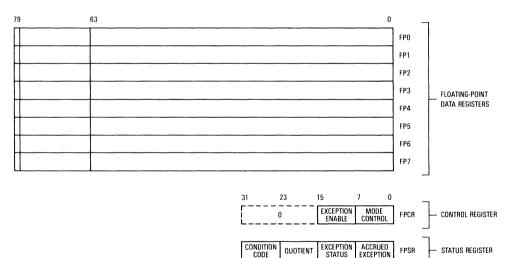

| 1-1              | MC68881/MC68882 Programming Model                               | 1-3            |

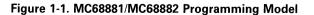

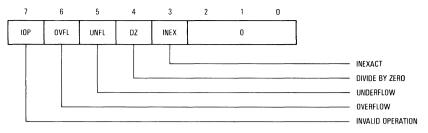

| 1-2              | Exception Status/Enable Byte                                    | 1-4            |

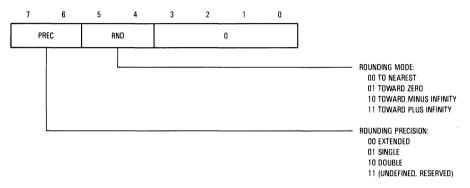

| 1-3              | Mode Control Byte                                               | 1-4            |

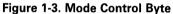

| 1-4              | Condition Code Byte                                             | 1-4            |

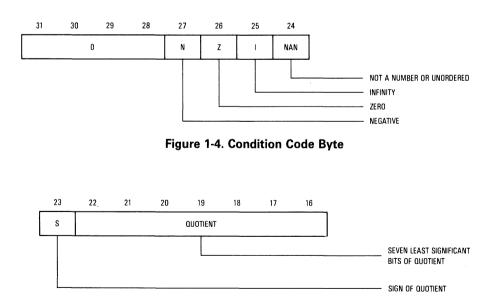

| 1-5              | Quotient Byte                                                   |                |

| 1-6              | Accrued Exception Byte                                          |                |

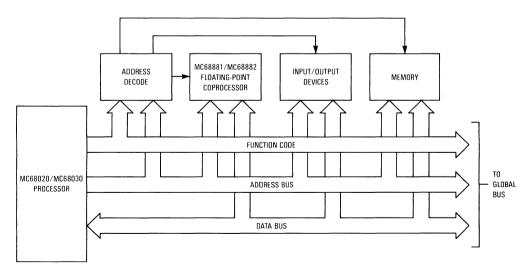

| 1-7              | Typical Coprocessor Configuration                               |                |

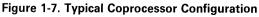

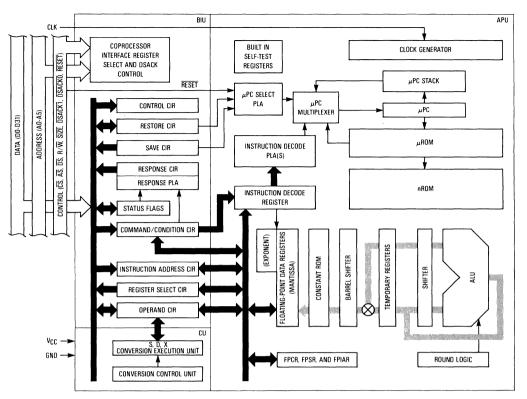

| 1-8              | MC68881 Simplified Block Diagram                                |                |

| 1-9              | MC68882 Simplified Block Diagram                                |                |

| 1-10             | MC68881/MC68882 Data Format Summary                             | 1-11           |

| 2-1              | MC68881/MC68882 Programming Model                               | 2-1            |

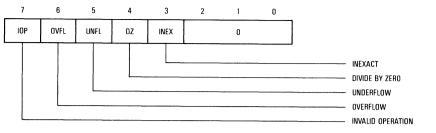

| 2-2              | MC68881/MC68882 FPCR Exception Enable Bye                       | 2-2            |

| 2-3              | MC68881/MC68882 FPCR Mode Control Byte                          |                |

| 2-4              | MC68881/MC68882 FPSR Condition Code Byte                        |                |

| 2-5              | MC68881/MC68882 FPSR Quotient Byte                              |                |

| 2-6              | MC68881/MC68882 FPSR Exception Status Byte                      |                |

| 2-7              | MC68881/MC68882 FPSR Accrued Exception Byte                     | 2-7            |

| 3-1              | Signed Integer Data Formats                                     |                |

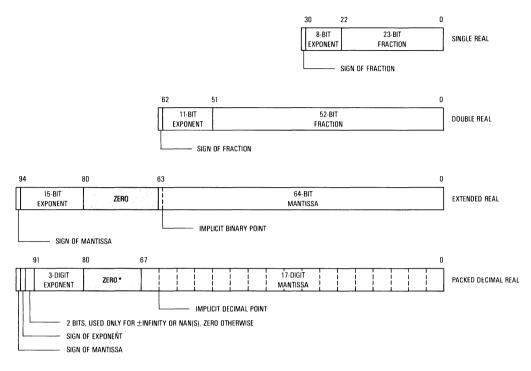

| 3-2              | Binary Real Data Formats                                        | 3-2            |

| 3-3              | Format of Normalized Numbers                                    |                |

| 3-4              | Format of Denormalized Numbers                                  |                |

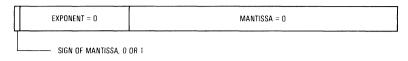

| 3-5              | Format of Zero                                                  |                |

| 3-6              | Format of Infinity                                              |                |

| 3-7              | Format of Not-A-Numbers                                         |                |

| 3-8              | Binary Real Data Type Summary                                   |                |

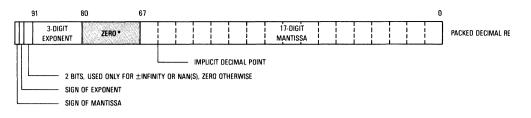

| 3-9              | Packed Decimal Real Data Format                                 |                |

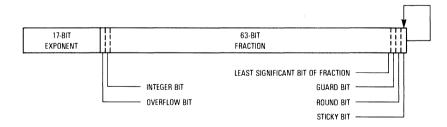

| 3-10             | Intermediate Result Format                                      |                |

| 3-11             | Packed Decimal Real Data Format Detail                          | 3-12           |

| 4-1              | Instruction Description Format                                  |                |

| 4-2              | Operation Table Example (FADD Instruction)                      | 4-13           |

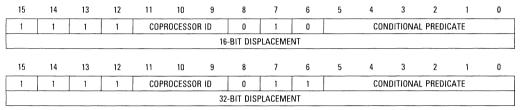

| 5-1              | MC68881 Concurrency — FMUL Instruction                          | 5-2            |

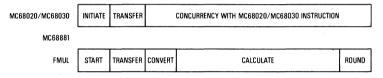

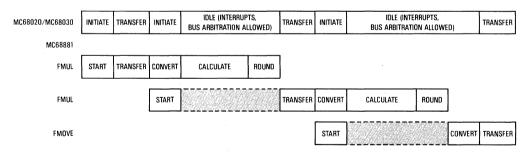

| 5-2              | MC68881 Concurrency - FMUL Followed by FMUL and FMOVE           |                |

| 5-3              | MC68882 Concurrency — FMUL Followed by FMUL and FMOVE           |                |

| 5-4              | Rolled Version of Linpack Loop                                  | 5-9            |

| 5-5              | Optimized Linpack Loop                                          |                |

| 5-6              | Minimum Exception Handler                                       |                |

| 5-7              | Idle State Frame Access Example                                 |                |

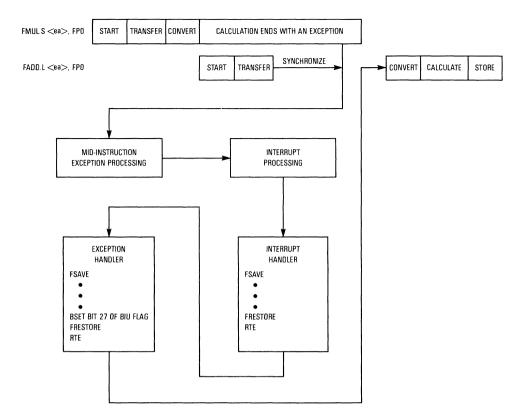

| 5-8              | Simultaneous Task Switch Interrupt and Floating-Point Exception | 5-14           |

| 5- <b>9</b>      | Coprocessor Identification Code                                 | 5-15           |

## LIST OF ILLUSTRATIONS (Continued)

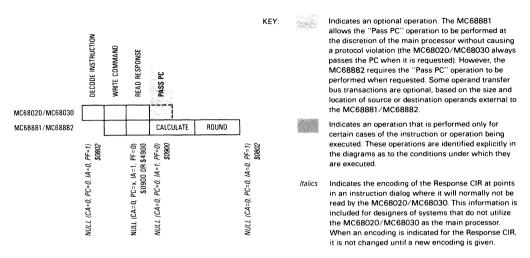

| 6-1EXC and ENABLE Byte Bit Assignments.6-46-2Intermediate Result Format.6-156-3Rounding Algorithm6-166-4MC68881 State Frame Formats6-296-5MC68882 State Frame Formats6-306-6BIU Flag Format6-326-7Full Context Save/Restore Instruction Sequences6-387-1MPU Address Bus Encoding for Coprocessor Accesses7-17-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-7MC68000 Coprocessor Response Primitive General Format7-97-8Null Primitive Format7-10 | Figure<br>Number | Title                                                                      | Page<br>Number |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------|----------------|

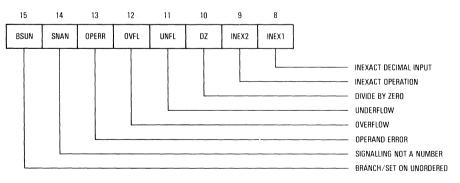

| 6-3Rounding Algorithm6-166-4MC68881 State Frame Formats6-296-5MC68882 State Frame Formats6-306-6BIU Flag Format6-326-7Full Context Save/Restore Instruction Sequences6-387-1MPU Address Bus Encoding for Coprocessor Accesses7-17-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                    | 6-1              | EXC and ENABLE Byte Bit Assignments                                        | 6-4            |

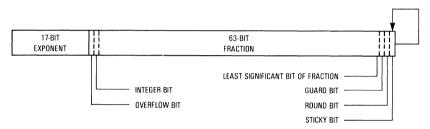

| 6-4MC68881 State Frame Formats6-296-5MC68882 State Frame Formats6-306-6BIU Flag Format6-326-7Full Context Save/Restore Instruction Sequences6-387-1MPU Address Bus Encoding for Coprocessor Accesses7-17-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                             | 6-2              | Intermediate Result Format                                                 | 6-15           |

| 6-5MC68882 State Frame Formats6-306-6BIU Flag Format6-326-7Full Context Save/Restore Instruction Sequences6-387-1MPU Address Bus Encoding for Coprocessor Accesses7-17-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                               | 6-3              |                                                                            |                |

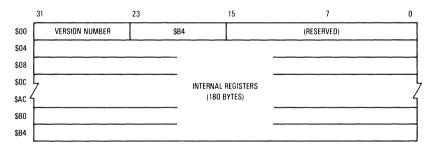

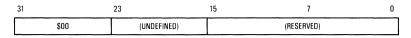

| 6-6BIU Flag Format6-326-7Full Context Save/Restore Instruction Sequences6-387-1MPU Address Bus Encoding for Coprocessor Accesses7-17-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                                                                 | 6-4              | MC68881 State Frame Formats                                                | 6-29           |

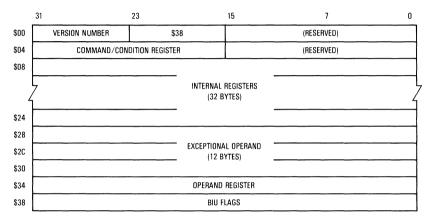

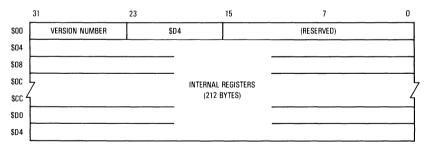

| 6-7Full Context Save/Restore Instruction Sequences6-387-1MPU Address Bus Encoding for Coprocessor Accesses7-17-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                                                                                       | 6-5              | MC68882 State Frame Formats                                                | 6-30           |

| 7-1MPU Address Bus Encoding for Coprocessor Accesses7-17-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                                                                                                                                             | 6-6              |                                                                            |                |

| 7-2FPCP Coprocessor Interface Register Map7-27-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                                                                                                                                                                                                    | 6-7              | Full Context Save/Restore Instruction Sequences                            | 6-38           |

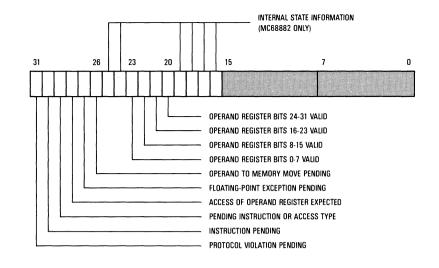

| 7-3Control CIR Register7-37-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                                                                                                                                                                                                                                                 | 7-1              | MPU Address Bus Encoding for Coprocessor Accesses                          | . 7-1          |

| 7-4Operand CIR Data Alignment7-77-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                                                                                                                                                                                                                                                                           | 7-2              | FPCP Coprocessor Interface Register Map                                    | 7-2            |

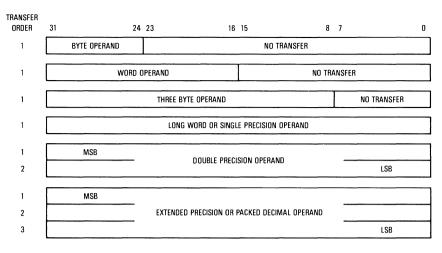

| 7-5Coprocessor Instruction General Format7-87-6FPCP Instruction Operation Word7-87-7MC68000 Coprocessor Response Primitive General Format7-9                                                                                                                                                                                                                                                                                                                                                                                                           | 7-3              | Control CIR Register                                                       | . 7-3          |

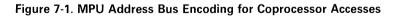

| <ul> <li>7-6 FPCP Instruction Operation Word</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7-4              |                                                                            |                |

| 7-7 MC68000 Coprocessor Response Primitive General Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-5              | Coprocessor Instruction General Format                                     | 7-8            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                                                                            |                |

| 7-8 Null Primitive Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-7              | MC68000 Coprocessor Response Primitive General Format                      | 7-9            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  | Null Primitive Format                                                      |                |

| 7-9 Evaluate Effective Address and Transfer Data Primitive Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | Evaluate Effective Address and Transfer Data Primitive Format              | . 7-12         |

| 7-10 Transfer Single Main Processor Register Primitive Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                                                                            |                |

| 7-11 Transfer Multiple Coprocessor Registers Primitive Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                                                                            |                |

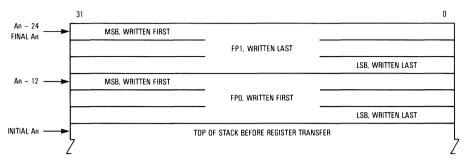

| 7-12 Transfer Multiple Floating-Point Data Register to Stack Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-12             | Transfer Multiple Floating-Point Data Register to Stack Example            | . 7-15         |

| 7-13 Take Pre-Instruction Exception Primitive Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | Take Pre-Instruction Exception Primitive Format                            | 7-16           |

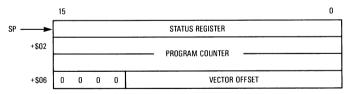

| 7-14 Pre-Instruction Exception Stack Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-14             |                                                                            |                |

| 7-15 Take Mid-Instruction Exception Primitive Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | Take Mid-Instruction Exception Primitive Format                            |                |

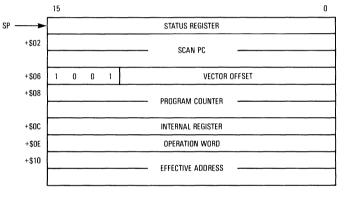

| 7-16 Mid-Instruction Stack Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  | Mid-Instruction Stack Frame                                                |                |

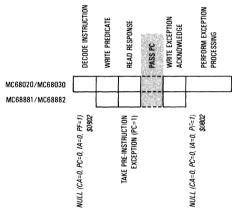

| 7-17 MC68881 Register-to-Register Instruction Dialog 7-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-17             |                                                                            |                |

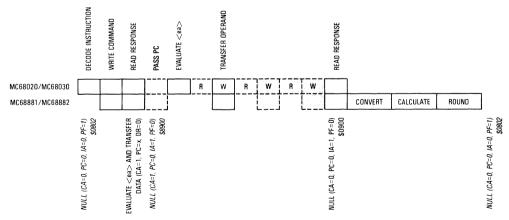

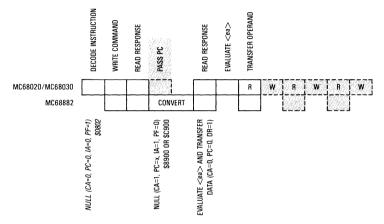

| 7-18 MC68881/MC68882 External-to-Register Instruction Dialog 7-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | MC68881/MC68882 External-to-Register Instruction Dialog                    | . 7-21         |

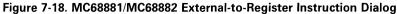

| 7-19 MC68882 External-to-Register Instruction Dialog 7-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  | MC68882 External-to-Register Instruction Dialog                            | . 7-22         |

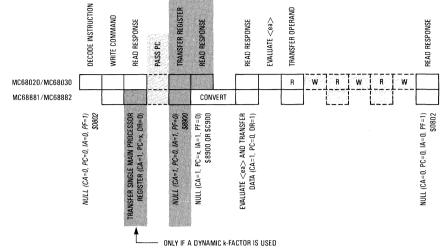

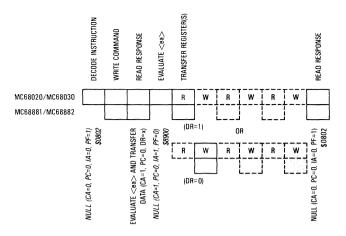

| 7-20 MC68881/MC68882 Register-to-External Instruction Dialog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |                                                                            |                |

| 7-21 MC68882 Register-to-External Instruction Dialog (S,D, and X Formats) 7-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | MC68882 Register-to-External Instruction Dialog (S,D, and X Formats)       |                |

| 7-22 Move Control Register Instruction Dialog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ·                |                                                                            |                |

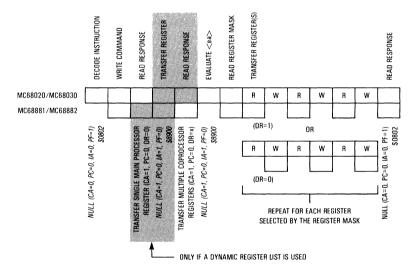

| 7-23 Move Multiple Floating-Point Data Registers Instruction Dialog 7-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                | Move Multiple Floating-Point Data Registers Instruction Dialog             | . 7-25         |

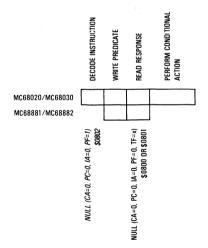

| 7-24 Conditional Instruction Dialog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | Conditional Instruction Dialog                                             | . 7-26         |

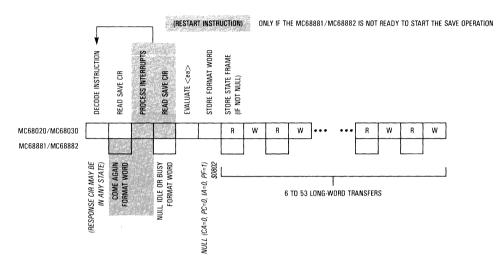

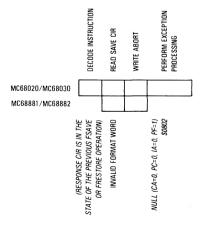

| 7-25 FSAVE Instruction Dialog 7-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | FSAVE Instruction Dialog                                                   |                |

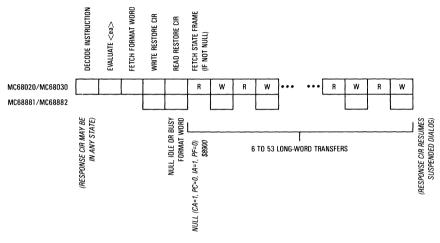

| 7-26 FRESTORE Instruction Dialog 7-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                                                                            |                |

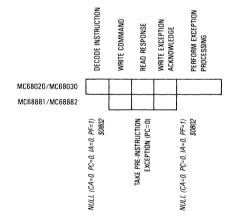

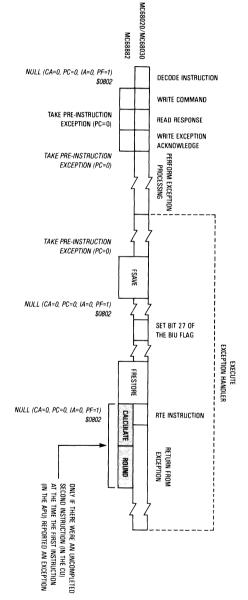

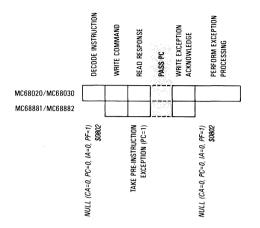

| 7-27 Take Pre-Instruction Exception Dialog — MC68881 7-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                                                                            |                |

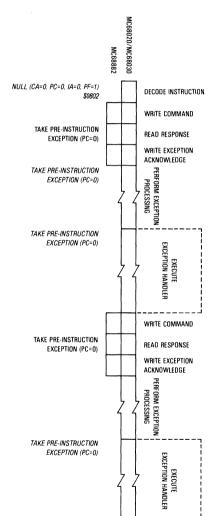

| 7-28 Take Pre-Instruction Exception Dialog — MC68882 7-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                                                                            | . 7-31         |

| 7-29 Take Pre-Instruction Exception Dialog — MC68882                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-29             |                                                                            | 7.04           |

| with No FSAVE Instruction in the Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7 00             |                                                                            | . 7-31         |

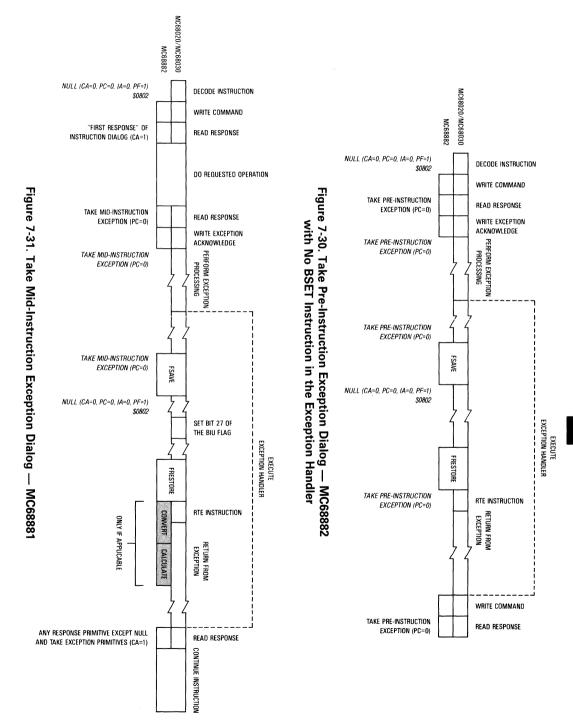

| 7-30 Take Pre-Instruction Exception Dialog — MC68882                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-30             |                                                                            |                |

| with No BSET Instruction in the Exception Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7.04             |                                                                            |                |

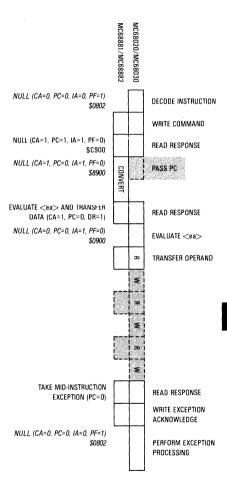

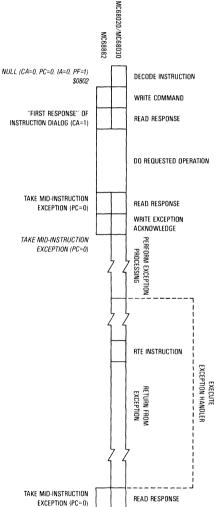

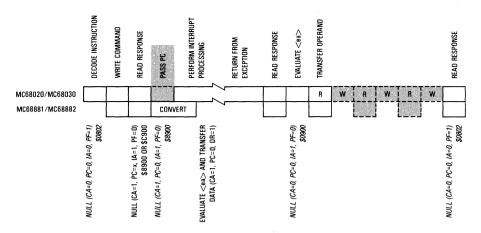

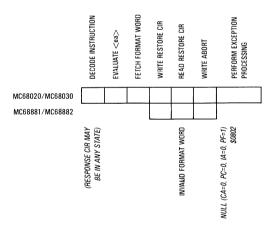

| 7-31 Take Mid-Instruction Exception Dialog — MC68881 7-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                                                                            | . 7-32         |

| 7-32 Take Mid-Instruction Exception Dialog — MC68882<br>General Concurrent Case                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-32             | Take Mid-Instruction Exception Dialog — MC68882<br>General Concurrent Case | 7-34           |

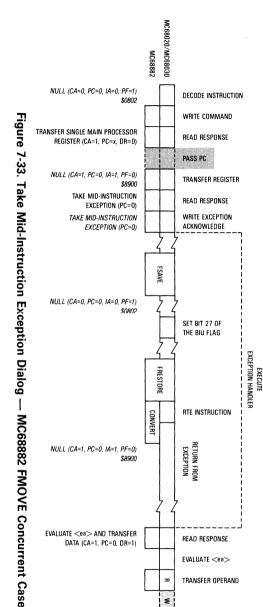

| 7-33 Take Mid-Instruction Exception Dialog — MC68882                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-33             | Take Mid-Instruction Exception Dialog — MC68882                            | . , 04         |

| FMOVE Concurrent Case 7-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7.04             | FMOVE Concurrent Case                                                      | . 7-34         |

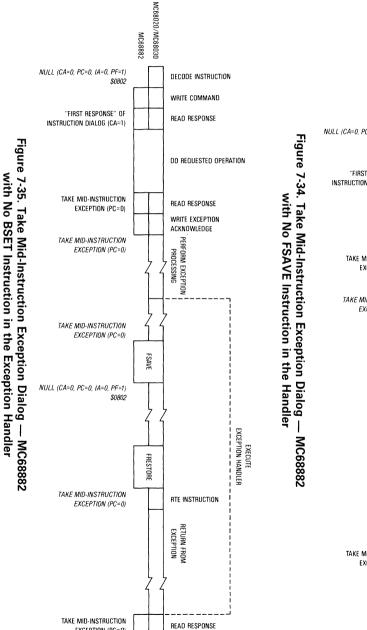

| 7-34 Take Mid-Instruction Exception Dialog — MC68882<br>with No FSAVE Instruction in the Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-34             |                                                                            | 7-35           |

## LIST OF ILLUSTRATIONS (Concluded)

| Figure<br>Number | Title                                                                        | Page<br>Number |

|------------------|------------------------------------------------------------------------------|----------------|

| 7-35             | Take Mid-Instruction Exception Dialog — MC68882                              |                |

| 7.00             | with No BSET Instruction in the Handler                                      |                |

| 7-36             | Mid-Instruction Interrupt Dialog                                             |                |

| 7-37             | Take BSUN Exception Dialog                                                   |                |

| 7-38<br>7-39     | Take F-Line Emulator Exception Dialog                                        |                |

| 7-39<br>7-40     | FSAVE Format Exception Dialog<br>FRESTORE Format Exception Dialog            |                |

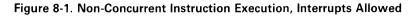

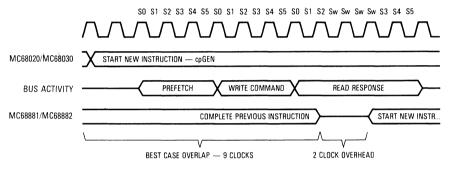

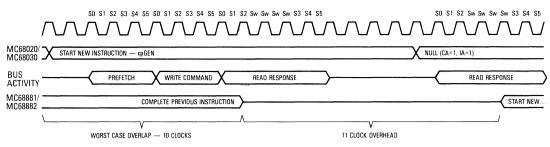

| 8-1              | Non-Concurrent Instruction Execution, Interrupts Allowed                     | . 8-5          |

| 8-2              | Best-Case Coprocessor Interface Overhead Timing                              |                |

| 8-3              | Worst-Case FPCP Interface Overhead Timing                                    |                |

| 8-4              | Instruction Overlap Examples — FMOVE.X FPm,FPn                               |                |

| 8-5              | Instruction Overlap Example — FMOVES.S (An),FPn                              | . 8-21         |

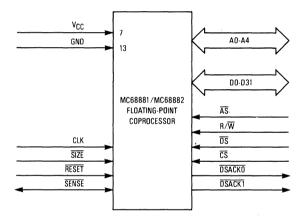

| 9-1              | MC68881/MC68882 Input/Output Signals                                         | . 9-1          |

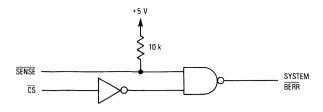

| 9-2              | Sense Device Circuit Example                                                 |                |

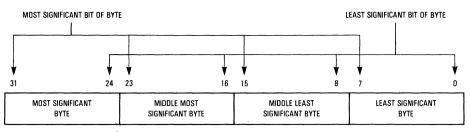

| 10-1             | FPCP Data Bus Bit Assignments                                                |                |

| 10-2             | Data Bus Activity vs Port Size and Operand Alignment                         |                |

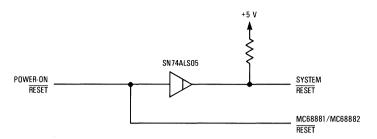

| 10-3             | FPCP Reset Logic Example                                                     |                |

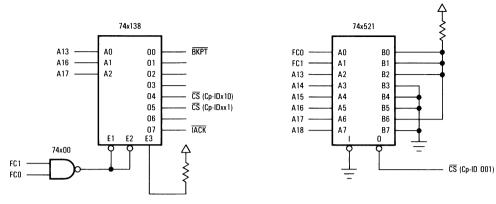

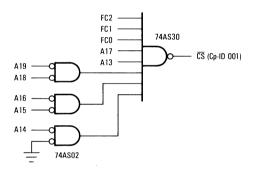

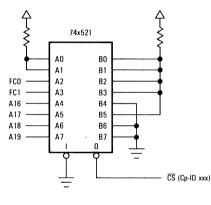

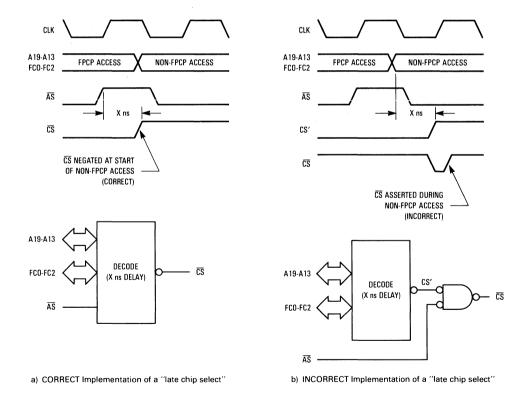

| 10-4<br>10-5     | Example of Early Chip Select Circuits<br>Example of Late Chip Select Circuit |                |

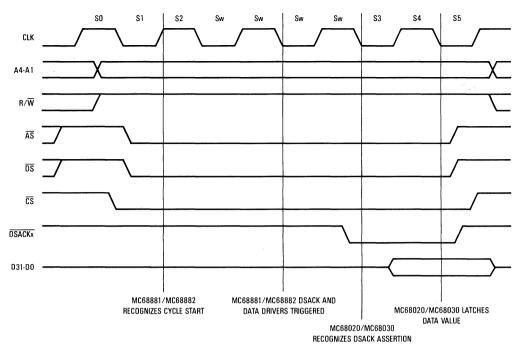

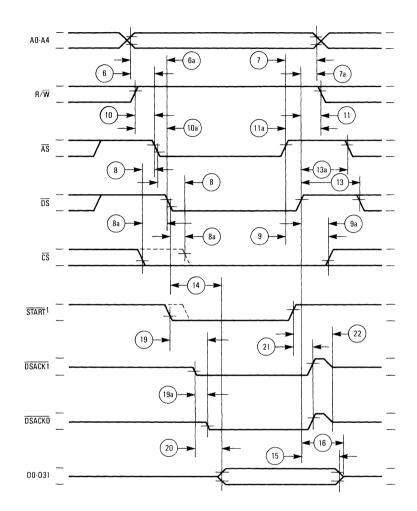

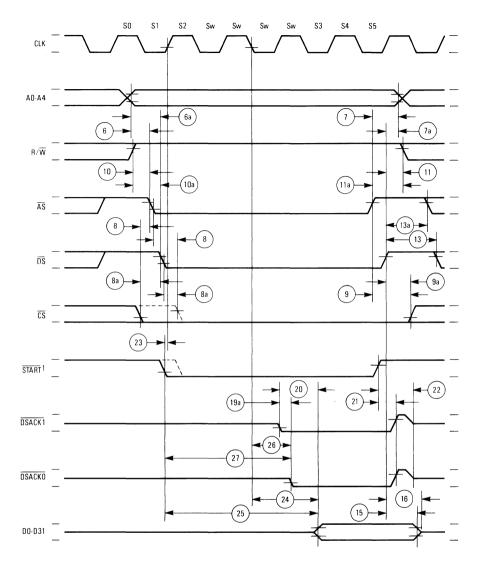

| 10-5             | Synchronous Read Cycle Timing Diagram                                        |                |

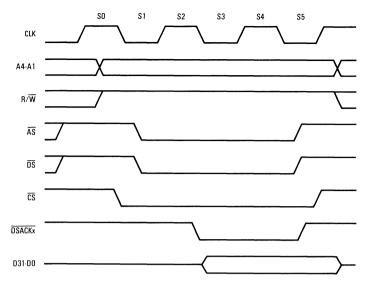

| 10-0             | Asynchronous Read Cycle Timing Diagram                                       |                |

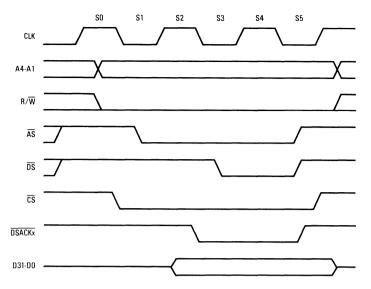

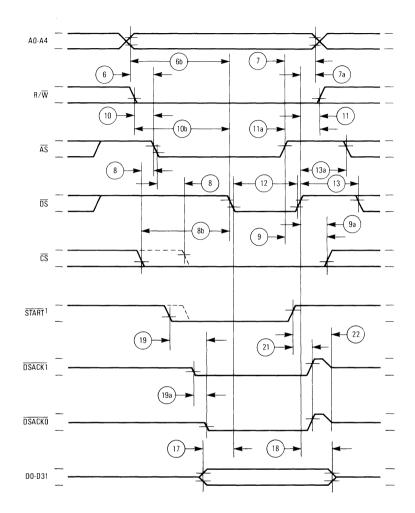

| 10-8             | Asynchronous Write Cycle Timing Diagram                                      |                |

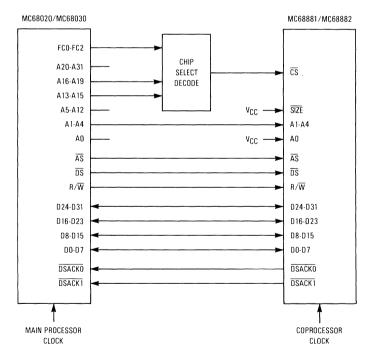

| 11-1             | 32-Bit Data Bus Coprocessor Connection                                       | . 11-1         |

| 11-2             | 16-Bit Data Bus Coprocessor Connection                                       |                |

| 11-3             | 8-Bit Data Bus Coprocessor Connection                                        |                |

| 11-4             | 16-Bit Data Bus Peripheral Processor Connection                              |                |

| 11-5             | 8-Bit Data Bus Peripheral Processor Connection                               | . 11-4         |

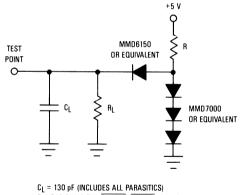

| 12-1             | Test Loads                                                                   |                |

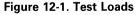

| 12-2<br>12-3     | Clock Input Timing Diagram                                                   |                |

|                  | Asynchronous Read Cycle Timing Diagram                                       | 1              |

| 12-4             | Asynchronous Write Cycle Timing Diagram                                      | .Foldout<br>2  |

| 12-5             | Synchronous Read Cycle Timing Diagram                                        |                |

4

. . .

## **LIST OF TABLES**

| Table<br>Number | Title                                                  | Page<br>Number |

|-----------------|--------------------------------------------------------|----------------|

| 1-1             | Exponent and Mantissa Sizes                            | 1-10           |

| 2-1             | Condition Code versus Result Data Type                 | 2-4            |

| 3-1             | Single Precision Binary Real Format                    |                |

| 3-2             | Double Precision Binary Real Format                    |                |

| 3-3             | Extended Precision Binary Real Format                  | 3-11           |

| 3-4             | Decimal String Type Definitions                        | 3-12           |

| 4-1             | Data Movement Operations                               |                |

| 4-2             | Dyadic Operation Format                                |                |

| 4-3             | Dyadic Operations                                      |                |

| 4-4             | Monadic Operation Format                               |                |

| 4-5             | Monadic Operations                                     |                |

| 4-6             | Dual Monadic Operation Format                          |                |

| 4-7             | Program Control Operations                             | 4-4            |

| 4-8             | Conditional Test Mnemonics                             | 4-4            |

| 4-9             | System Control Operations                              | 4-5            |

| 4-10            | Effective Addressing Mode Categories                   |                |

| 4-11            | General Type Instruction Command Word Fields           | 4-121          |

| 4-12            | Register Field Encoding                                | 4-122          |

| 4-13            | Extension Field Encoding for Arithmetic Operations     | 4-123          |

| 4-14            | Source Format Field Encoding                           |                |

| 4-15            | Destination Format Field Encoding                      |                |

| 4-16            | Extension Field Encoding                               |                |

| 4-17            | Encoding for Move FPcr Operations                      |                |

| 4-18            | Encodings for Move Multiple FPn Operations             |                |

| 4-19            | Encodings for the FDBcc, FScc, and FTRAPcc Instuctions |                |

| 4-20            | Conditional Predicate Evaluation Responses             |                |

| 4-21            | Effective Address Field Encoding Summary               |                |

| 4-22            | Conditional Predicate Field Encoding Summary           |                |

| 5-1             | Minimum-Concurrency Instructions                       | 5-3            |

| 5-2             | Monadic Instructions                                   |                |

| 5-3             | Dyadic Operations                                      |                |

| 5-4             | Partial-Concurrency Instructions                       |                |

| 5-5             | Fully-Concurrent Instructions                          |                |

| 5-6             | Conditional Instructions.                              |                |

| 5-7             | FMOVE Instruction Execution Times                      |                |

| 5-8             | State Frame Sizes                                      |                |

| 00              |                                                        |                |

| 6-1             | MC68881/MC68882 Exception Vector Assignments           |                |

| 6-2             | Possible Operand Errors                                | 6-7            |

## LIST OF TABLES (Continued)

| Table<br>Number | Title                                                                                                        | Page<br>Number |

|-----------------|--------------------------------------------------------------------------------------------------------------|----------------|

| 6-3             | Possible Divide-by-Zero Exceptions                                                                           | 6-13           |

| 6-4             | BIU Flag Bit Definitions                                                                                     |                |

| 6-5             | MC68881/MC68882 Responses to Save Command                                                                    |                |

| 6-6             | MC68881/MC68882 Format Word Definitions                                                                      | 6-35           |

| 7-1             | MPU CPU Space Type Field Encoding                                                                            |                |

| 7-2             | Coprocessor Interface Register Characteristics                                                               |                |

| 7-3             | Null Primitive Encodings                                                                                     |                |

| 7-4<br>7-5      | Coprocessor Valid Effective Address Codes<br>Evaluate Effective Address and Transfer Data Primitive Encoding |                |

| 7-5<br>7-6      | FPCP Vector Numbers                                                                                          |                |

| 7-0             | MC68881/MC68882 Primitive Responses                                                                          | -              |

|                 |                                                                                                              |                |

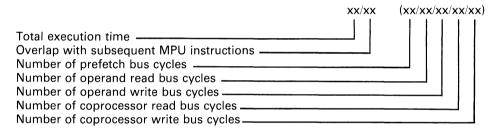

| 8-1             | Effective Address Calculations                                                                               | . 8-11         |

| 8-2             | MC68881 Overall Execution Times                                                                              |                |

| 8-3             | MC68882 Overall Execution Times                                                                              |                |

| 8-4             | Bus Cycle Activity — Arithmetic Operations                                                                   |                |

| 8-5             | Timing Calculation Example                                                                                   |                |

| 8-6             | Move Control Register and MOVEM Execution Times                                                              |                |

| 8-7             | Conditional Instruction Execution Times<br>FSAVE and FRESTORE Instruction Execution Times                    |                |

| 8-8<br>8-9      | Instruction Start-Up Times                                                                                   |                |

| 8-3<br>8-10     | Null Primitive Time Values                                                                                   |                |

| 8-10<br>8-11    | Operand Transfer Time — External Operand                                                                     |                |

| 8-12            | Operand Transfer Time — Immediate Operand                                                                    |                |

| 8-13            | Input Operand Conversion                                                                                     |                |

| 8-14            | Arithmetic Calculation Times — Dyadic Operations                                                             |                |

| 8-15            | Arithmetic Calculation Times — Monadic Operations                                                            | . 8-30         |

| 8-16            | Output Operand Conversion                                                                                    | . 8-31         |

| 8-17            | Output Operand Conversion — Binary Real Formats                                                              | . 8-31         |

| 8-18            | Rounding Operation Time Values                                                                               |                |

| 8-19            | Exception Handling Time Values                                                                               |                |

| 8-20            | Conditional Termination Times Values                                                                         |                |

| 8-21            | Multiple Register Transfer Time Values                                                                       |                |

| 8-22<br>8-23    | State Frame Transfer Time Values                                                                             |                |

| 8-23<br>8-24    | Instruction Termination Processing Time Values<br>Exception Processing Time Values                           |                |

| 8-24<br>8-25    | Overlap Allowed Times — Arithmetic Operations                                                                |                |

| 025             |                                                                                                              |                |

| 9-1             | Coprocessor Interface Register Selection                                                                     | . 9-2          |

| 9-2             | System Data Bus Size Configuration                                                                           |                |

| 9-3             | DSACK Assertions                                                                                             |                |

| 9-4<br>9-5      | VCC and GND Pin Assignments                                                                                  |                |

| 9-9             | Signal Summary                                                                                               | . 9-0          |

### SECTION 1 GENERAL DESCRIPTION

The MC68881 and MC68882 floating-point coprocessors (FPCP) both fully implement the *IEEE Standard for Binary Floating-Point Arithmetic* (ANSI-IEEE Std 754-1985) for use with the Motorola M68000 Family of microprocessors. The coprocessors are both implemented in VLSI technology to give systems designers the highest possible functionality in a physically small device. The MC68882 provides an increased level of performance in a coprocessor that is fully compatible and physically interchangeable with the MC68881.

Intended primarily for use as coprocessors to the MC68020/MC68030 32-bit microprocessor unit (MPU), the MC68881 and MC68882 provide a logical extension to the main processing unit integer data processing capabilities. These coprocessors provide a very high performance floating-point arithmetic unit and a set of floating-point data registers utilized in a manner that is analogous to the use of the integer data registers. The MC68881/MC68882 instruction set, a natural extension of all earlier members of the M68000 Family, supports all of the addressing modes of the host MPU. Due to the flexible bus interface of the M68000 Family, the MC68881 or MC68882 can be used with any of the MPU devices of the family and may also be used as a peripheral to other processors.

The major features of the MC68881 and MC68882 are:

- Eight general purpose floating-point data registers, each supporting a full 80-bit extended precision real data format (a 64-bit mantissa plus a sign bit, and a 15-bit signed exponent).

- A 67-bit arithmetic unit to allow very fast calculations, with intermediate precision greater than the extended precision format.

- A 67-bit barrel shifter for high-speed shifting operations (for normalizing, etc.).

- Forty-six instructions, including 35 arithmetic operations.

- Full conformance to the ANSI-IEEE 754-1985 standard, including all requirements and suggestions.

- Support of functions not defined by the IEEE standard, including a full set of trigonometric and transcendental functions.

- Seven data formats: byte, word, and long word integers; single, double, and extended precision real numbers; and packed binary coded decimal string real numbers.

- Twenty-two constants available in the on-chip ROM, including  $\pi$ , e, and powers of 10.

- Virtual memory/machine operations.

- Efficient mechanisms for exception processing, context switches, and interrupt handling.

- Fully concurrent instruction execution with the main processor.

- Use with any host processor, on an 8-, 16-, or 32-bit data bus.

In addition to these features, the MC68882 provides:

- Concurrent execution of multiple floating-point instructions.

- Special purpose hardware for high-speed conversion of binary real memory operands to/ from the internal extended format.

- Simultaneous access to the floating-point registers by the MC68882's conversion and arithmetic processing units.

- Reduced coprocessor interface overhead to increase throughput.

#### **1.1 THE COPROCESSOR CONCEPT**

1

The FPCP functions as a coprocessor in systems where the MC68020 or MC68030 is the main processor via the M68000 coprocessor interface. It functions as a peripheral processor in systems where the main processor is the MC68000, MC68008, or MC68010.

The FPCP utilizes the M68000 Family coprocessor interface to provide a logical extension of the MPU registers and instruction set in a manner that is transparent to the programmer. The programmer perceives the MPU and FPCP execution model as if both devices were implemented on one chip.

A fundamental goal of the M68000 Family coprocessor interface is to provide the programmer with an execution model based upon sequential instruction execution by the MPU and the FPCP. For optimum performance, however, the coprocessor interface allows floating-point instructions to execute concurrently with MPU integer instructions. Concurrent instruction execution is further extended by the MC68882, which can execute multiple floating-point instructions simultaneously. However, the coprocessor interface and the FPCP are designed to maintain a strictly sequential instruction execution model from the programmer's viewpoint.

The FPCP is a non-DMA type coprocessor that uses a subset of the general purpose coprocessor interface supported by the MPU. Features of the interface implemented in the FPCP are as follows:

- The main processor and the FPCP communicate via standard M68000 bus cycles.