Data Book

# AT&T WE® 32-Bit Microprocessors and Peripherals

August 1987

August 1987

# AT&T WE <sup>®</sup> 32-Bit Microprocessors and Peripherals Data Book

# A Word About Trademarks . . .

The following products mentioned in this Data Book are identified with AT&T trademarks:

WE<sup>®</sup> 32100 Microprocessor WE® 32200 Microprocessor WE® 32101 Memory Management Unit WE® 32201 Memory Management Unit WE ® 32102 Clock WE® 32103 DRAM Controller WE® 32104 DMA Controller WE<sup>®</sup> 32204 DMA Controller WE® 32106 Math Acceleration Unit WE® 32206 Math Acceleration Unit WE® 321AP Microprocessor Analysis Pod WE® 321DM CPU & MMU Device Monitor WE® 322DM CPU & MMU Device Monitor WE® 321DM-SP Device Monitor Software Programs WE® 321DS Microprocessor Development System WE® 321EB Microprocessor Evaluation Board WE® 321SB VMEbus Single Board Computer WE® 321SB-VFG Firmware Generation Programs WE® 321SB-VSD Software Debug Utility Programs WE® 321SD Development Software Programs WE® 321SE Evaluation Software Programs WE® 321SG Software Generation Programs WE® 321SG C-Software Generation Programs WE® 321SG Cross C-Software Generation Programs WE® 321SG-CUX Cross UNIX System Software Generation Programs WE® 321SG-CRS Cross Software Generation Programs WE® 321SG-NAT Native Software Generation Programs WE® 32-Bit Microprocessors and Peripherals UNIX® Operating System, System V, System V/VME, or System

VAX<sup>®</sup> 11/780 Computer is a registered trademark of Digital Equipment Corporation MS-DOS<sup>®</sup> is a registered trademark of the Microsoft Corporation

# Data Sheets Status Markings ...

Data sheets without a status marking are final and are issued when tool made samples are approved or when the product is delivered for usage, whichever comes first. The other data sheet status markings used throughout this catalog are defined as:

Advance – Issued at the exploratory stage of development when the principle characteristics are available. Some functional characteristics are subject to change.

**Preliminary** – Issued after development for manufacture has been started. Some electrical and timing parameters are subject to change.

# AT&T WE <sup>®</sup> 32-Bit Microprocessors and Peripherals Data Book

# Chapter 1. General

| Introduction                                     | 1-1 |

|--------------------------------------------------|-----|

| The System                                       | 1-1 |

| The WE 32100/32200 Microprocessors               | 1-1 |

| Peripheral Devices                               |     |

| Hardware/Software Support Tools                  | 1-2 |

| Board-Level Products                             |     |

| Development Software                             | 1-3 |

| Operating System Software                        | 1-3 |

| Quality Control and Reliability                  | 1-4 |

| Quality Control and Reliability                  | 1-4 |

| Reliability                                      | 1-4 |

| High Temperature Operating Bias/High Temperature |     |

| High Bias (HTOB/HTHB)                            | 1-4 |

| Temperature Humidity Bias (THB)                  | 1-5 |

| Temperature Cycling (TC)                         | 1-5 |

| Handling                                         |     |

| Integrated Circuits                              | 1-5 |

| Board-Level Products                             | 1-5 |

| Diskettes                                        |     |

| Military Specification Devices                   | 1-6 |

| Assistance                                       | 1-6 |

| Warranties                                       | 1-7 |

# Chapter 2. Devices

| WE | 32100 | Microprocessor                            | 2-1  |

|----|-------|-------------------------------------------|------|

| WE | 32200 | Microprocessor                            | 2-65 |

|    |       | Memory Management Unit                    |      |

|    |       | Memory Management Unit                    |      |

|    |       | Clock                                     |      |

|    |       | DRAM Controller                           |      |

|    |       | DMA Controller                            |      |

|    |       | DMA Controller                            |      |

|    |       | Math Acceleration Unit                    |      |

|    |       | Math Acceleration Unit                    |      |

|    |       | Microprocessors and Peripherals Packaging |      |

# Chapter 3. Development Support Tools

| WE 321DM CPU & MMU Device Monitor          | 3-1 |

|--------------------------------------------|-----|

| WE 322DM CPU & MMU Device Monitor          | 3-5 |

| WE 321DS Microprocessor Development System |     |

| WE 321EB Microprocessor Evaluation Board   |     |

# Chapter 4. Board-Level Products

| WE 321SB VMEbus Single Board | Computer | 4-1 | 1 |

|------------------------------|----------|-----|---|

|------------------------------|----------|-----|---|

# Chapter 5. Support Software

| WE 321SG Software Generation Programs Version 1.1            | 5-1  |

|--------------------------------------------------------------|------|

| WE 321SG C-Software and Cross C-Software Generation Programs |      |

| Version 2.0                                                  | 5-5  |

| UNIX System V Release 2.1/3.1                                | 5-9  |

| UNIX System V/VME                                            | 5-11 |

# Chapter 6. Training

| Training             | 6-1 |

|----------------------|-----|

| Educational Programs | 6-1 |

# Chapter 7. Ordering Information

| Ordering Information | 7-1 |

|----------------------|-----|

| Documentation        | 7-2 |

# **Device Alphanumeric Index**

| WE 32100 Microprocessor         | <br>2-1   |

|---------------------------------|-----------|

| WE 32101 Memory Management Unit | <br>2-145 |

| WE 32102 Clock                  |           |

| WE 32103 DRAM Controller        |           |

| WE 32104 DMA Controller         | 2-313     |

| WE 32106 Math Acceleration Unit |           |

| WE 32200 Microprocessor         | <br>3-65  |

| WE 32201 Memory Management Unit |           |

| WE 32204 DMA Controller         |           |

| WE 32206 Math Acceleration Unit |           |

# Introduction

# The System

This data book contains technical information about the AT&T WE 32-Bit Microprocessors and their support systems. The support systems consist of peripheral devices, single board products, software, hardware/software support tools, documentation, educational programs, and applications assistance.

The AT&T WE 32-Bit Microprocessors and Peripherals offer a complete package of devices and design tools that can speed up design time and get your product to the market in a timely and efficient manner. The AT&T WE 32-Bit Microprocessor chip set is the only one with 100 percent CMOS technology for low power consumption and compact designs. It offers glue-free interconnections and keeps device count, development time, and overall system costs to a minimum.

Each microprocessor and peripheral is built for the high-speed performance expected from a 32-bit system, supporting multi-user, multitasking applications. Designed to evolve into a new generation product with even higher performance, using the AT&T *WE* 32-Bit Microprocessor chip set ensures that the system being designed will be as current in the future as it is today.

The chip set, designed with the UNIX operating system in mind, offers the best hardware support possible for the world's most productive operating system. UNIX System V offers a highly optimized C language compiler, and can be used with other compilers for high level languages such as FORTRAN, COBOL, Pascal, and BASIC. These capabilities make UNIX System V the best development environment for 32-bit applications. Due to its flexibility, the AT&T WE 32-Bit Microprocessor chip set can be used to design a variety of products. You can offer a wide range of products from a single-user, low-priced version to high-performance, multi-user systems. Your initial design can be expanded or easily modified at any time, extending the life cycle of your product to accommodate new and changing technologies.

### The WE<sup>®</sup> 32100/32200 Microprocessors

The WE 32100/32200 Microprocessors are high-performance, single-chip, 32-bit central processing units (CPUs) designed for efficient operation in a high-level language environment. These microprocessors represent a state-ofthe-art concept in microprocessor architecture, providing one of the most powerful and extensive instruction sets available with any microprocessor.

Applications for these processors can be configured at the chip level or at the board level. At either level, the support system makes application design manageable and cost effective.

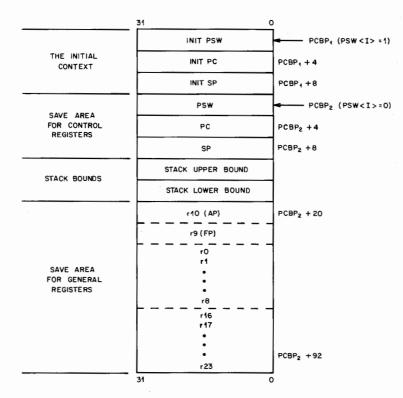

The WE 32200 Microprocessor is protocol and upward object code compatible with the WE 32100 CPU, and object code generated for the WE 32100 CPU will run without modification on the WE 32200 CPU. Enhancements designed into the WE 32200 Microprocessor include thirty-two 32-bit registers (the WE 32100 CPU has sixteen), expanded instruction set, expanded addressing modes, and byte replication on writes. Another feature, arbitrary byte alignment, allows the WE 32200 CPU to efficiently handle nonaligned memory accesses for both reads and writes. The WE 32200 CPU also utilizes dynamic bus sizing, allowing communication with both 16-bit and 32-bit memories and peripherals.

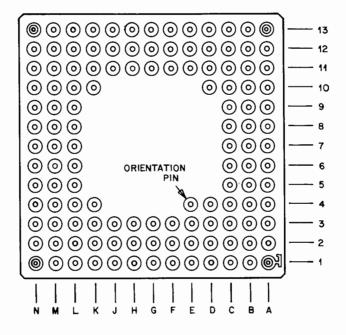

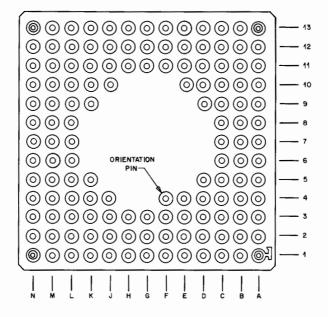

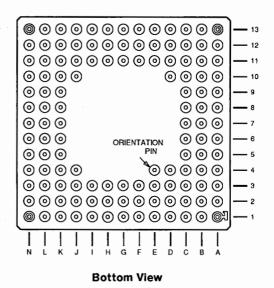

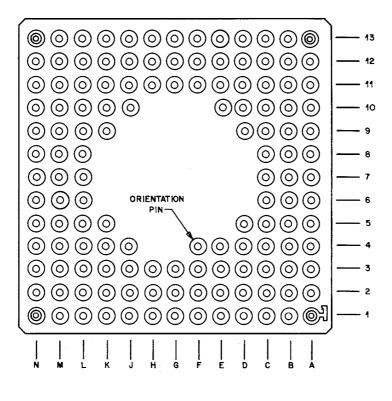

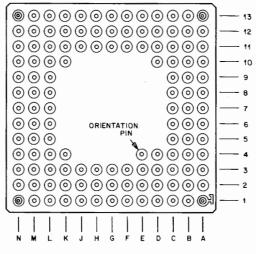

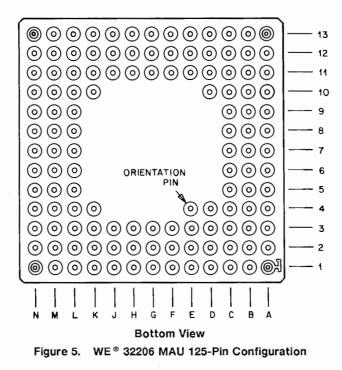

The WE 32100 Microprocessor is implemented in 1.0-micron CMOS technology and is packaged in a 125-pin square, ceramic pin grid array (PGA). It is available in 10-, 14-, and 18-MHz frequency versions.

The WE 32200 Microprocessor is implemented in 1.0-micron CMOS technology and is packaged in a 133-pin square, ceramic PGA. It is available in 24-MHz and higher frequency versions.

# **Peripheral Devices**

The essential components of a microcomputer include a central processing unit, memory, and input/output circuitry. The peripheral devices provide the interfacing, wait-state generation, and additional circuitry needed to support the processor in its microcomputer application.

#### Introduction

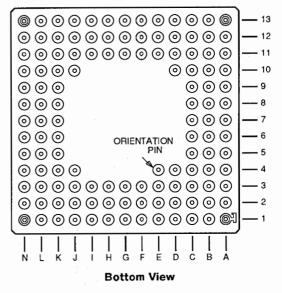

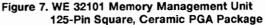

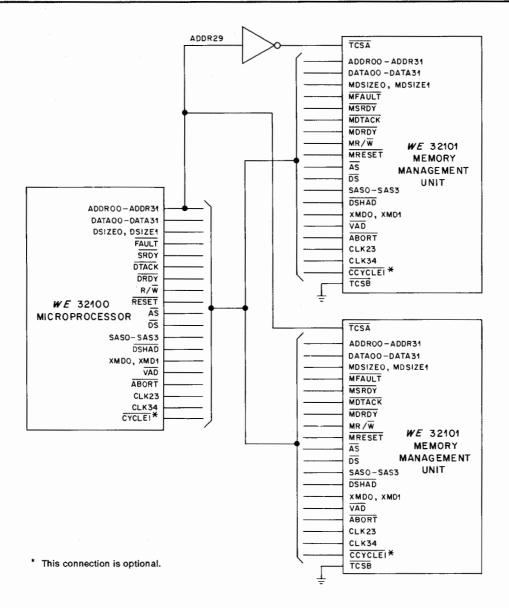

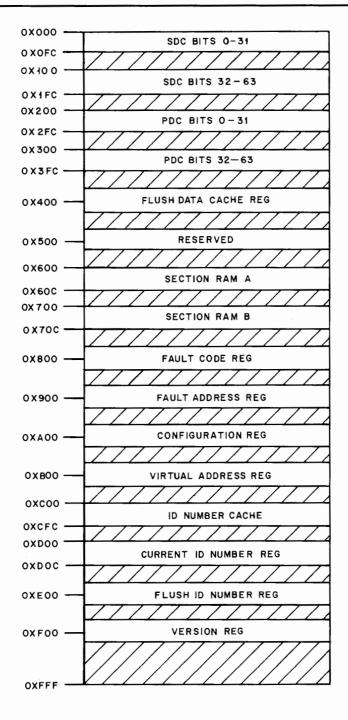

The WE 32101 Memory Management Unit (MMU) and the WE 32201 MMU provide logical-to-physical address translations, memory organization, and control and access protection for the microprocessors.

Advantages of the WE 32201 MMU over the WE 32101 MMU include a 4-Kbyte data/instruction cache; an on-chip, fully associative, content addressable memory (CAM) based, 64-entry descriptor cache; transparent multiple-context support; a flexible translation probe; and variable page sizes.

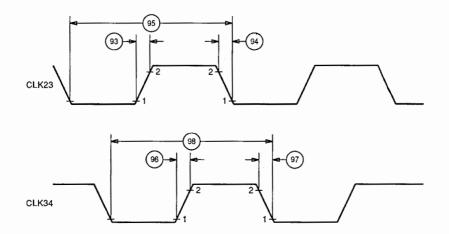

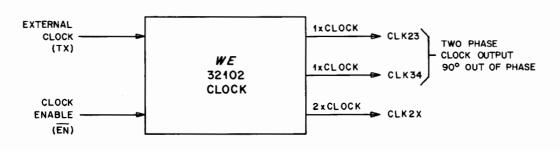

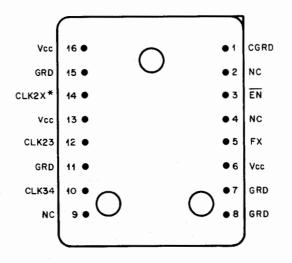

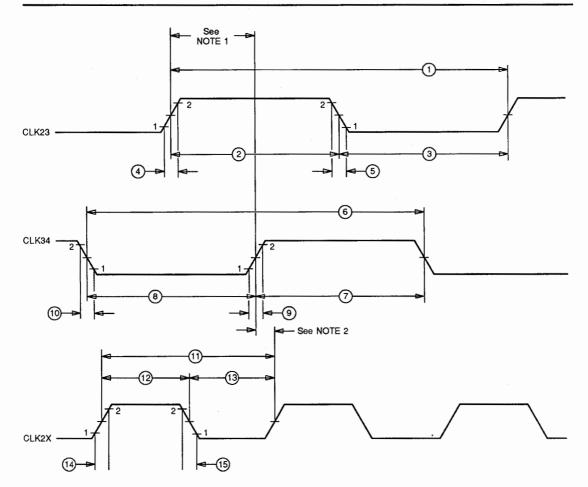

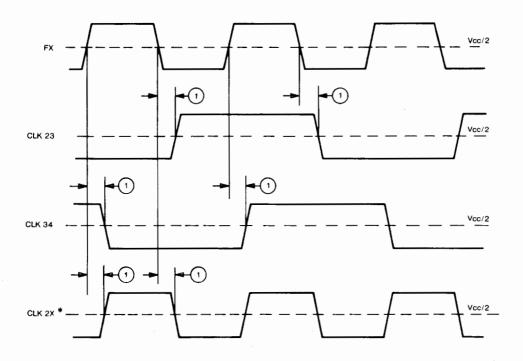

The WE 32102 Clock supplies the two-phase, CMOS-level frequency source required by the 32-bit microprocessors chip set. It is available at operating frequencies of 10, 14, 18, and 24 MHz and higher.

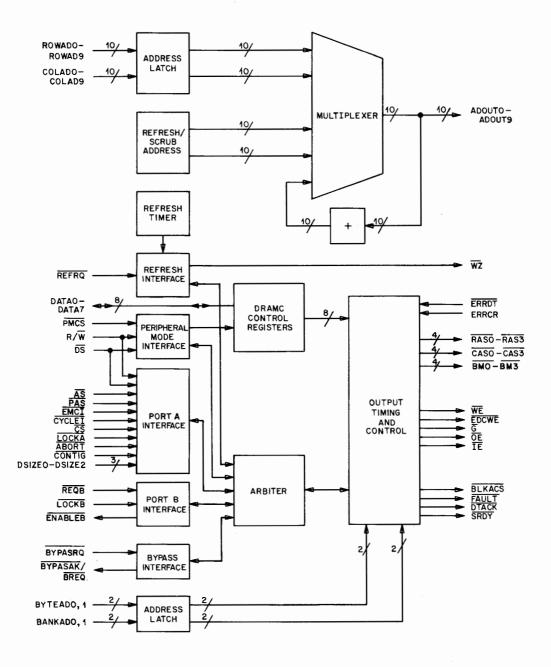

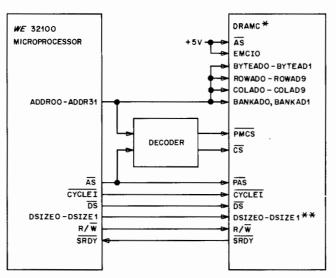

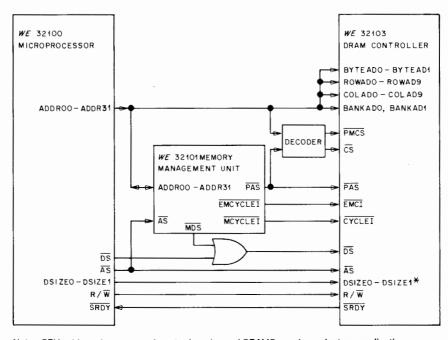

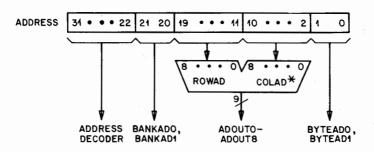

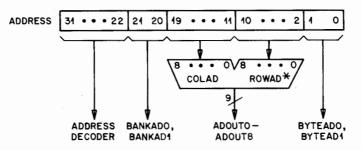

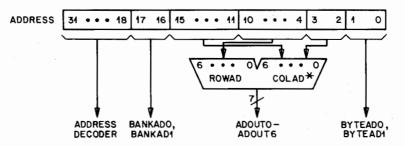

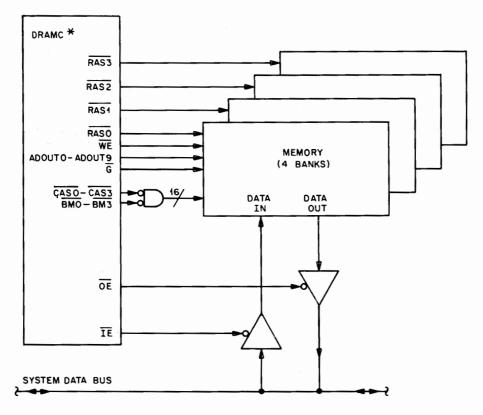

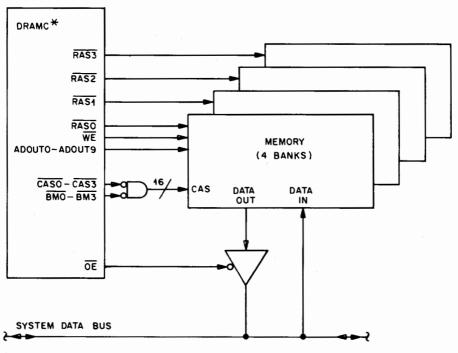

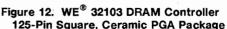

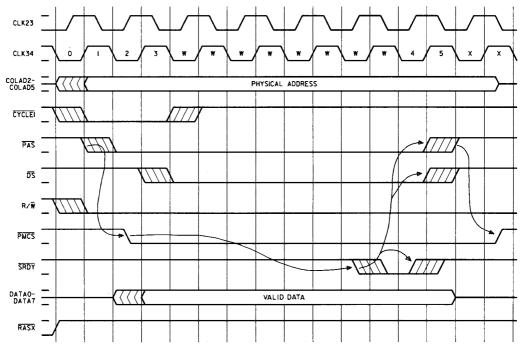

The WE 32103 DRAM Controller provides address multiplexing, access and cycle time management, and refresh control for dynamic random access memory (DRAM). The DRAM Controller is capable of addressing up to 16 Mbytes of DRAM, using 1 Mbit memory devices.

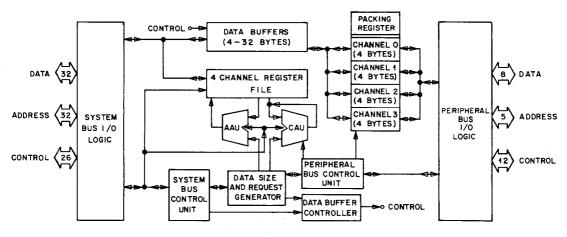

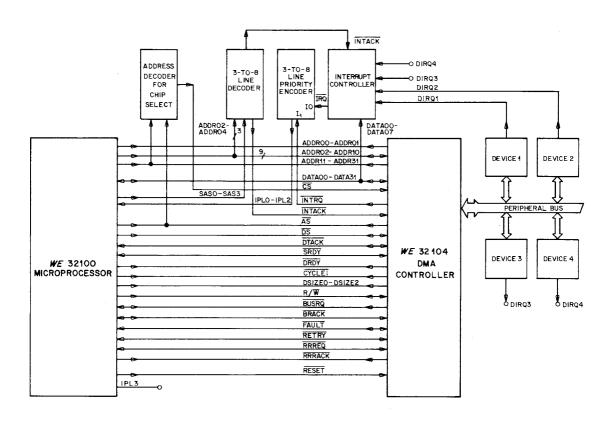

The WE 32104 DMA Controller (DMAC) is a memory-mapped peripheral device that performs direct memory-to-memory, memory-to-peripheral, and peripheral-to-memory data transfers quickly and efficiently. Specialized hardware permits these transfers at a rate much faster than a typical CPU.

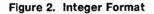

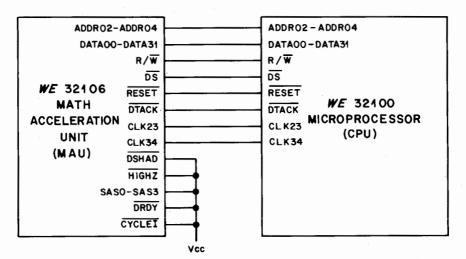

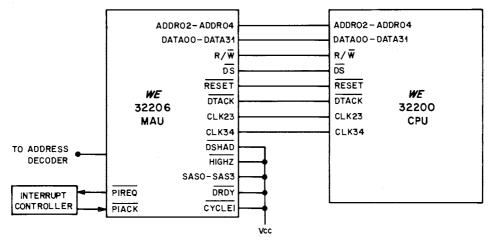

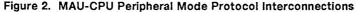

The WE 32106 Math Acceleration Unit (MAU) and the WE 32206 MAU provide floating-point capability for the WE 32100/32200 Microprocessors. Both MAUs are fully compatible with ANSI/IEEE Standard 754-1985 for Binary Floating-Point Arithmetic, and provide single, double, and double-extended precision capabilities.

The WE 32206 MAU is footprint, protocol, and upward object code compatible with the WE 32106 MAU. In addition, the WE 32206 MAU has eight 80-bit user registers (the WE 32106 MAU has four). The transcendental functions (sine, cosine, and arctangent) and pi have also been added to the WE 32206 MAU's instruction set.

#### Hardware/Software Support Tools

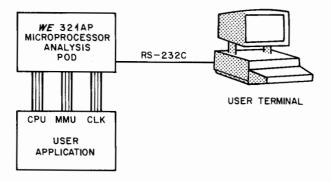

The WE 321DS Microprocessor Development

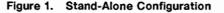

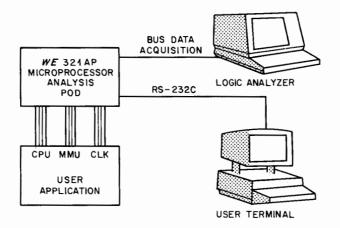

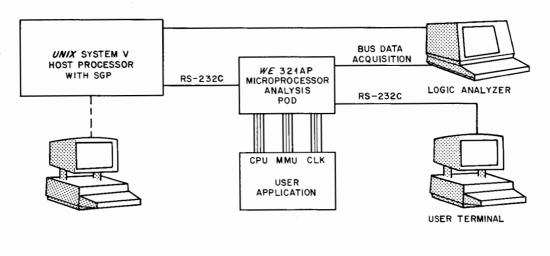

System is an integrated collection of hardware and software components used to develop, test, and debug applications based on the WE 32100 Microprocessor. Development System components include the WE 321AP Microprocessor Analysis Pod, the WE 321SD Development Software Programs, a UNIX System host, a high-level symbolic debugger, bus state analysis software, and a logic analyzer. The modular architecture of the Development System permits the user to configure the Analysis Pod, UNIX System host, and logic analyzer into any of four work stations that emphasize either hardware testing, software testing, or hardware/software integration and testing.

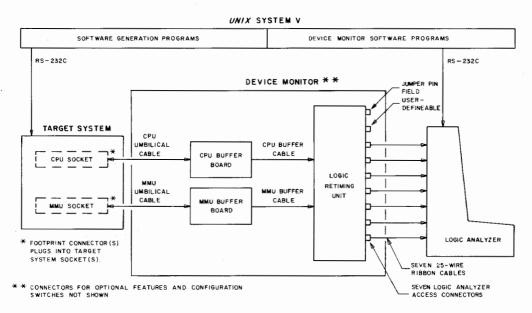

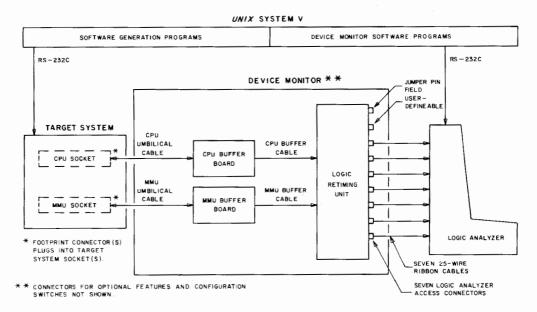

The WE 321DM/322DM CPU & MMU Device Monitors provide a low cost solution for debugging applications based on the WE 32100/32200 Microprocessors with a logic analyzer that is limited to a maximum sample rate of 10 MHz.

The device monitor consists of a logic retiming unit, a CPU cable system, an MMU cable system, and additional cables that provide a standard interface to a logic analyzer. The CPU and MMU cable systems contain footprint connectors that replace the CPU and MMU devices in the target system. The WE 321DM-SP Device Monitor Software Programs, supplied with the device monitor, provide for symbolic tracing and disassembly with the logic analyzer. This software includes three program trace disassemblers, configuration files, logic analyzer upload and download utilities, a symbol table utility, and a communication file for communication between the host UNIX System and the logic analyzer.

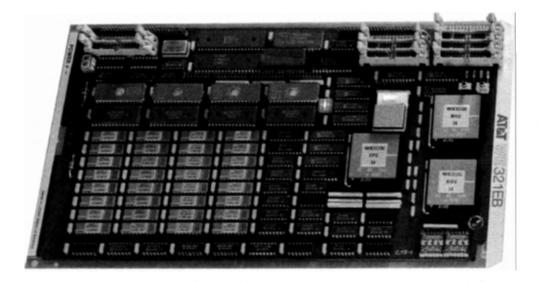

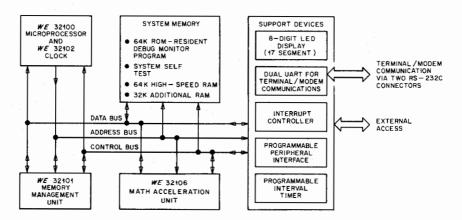

The WE 321EB Microprocessor Evaluation Board is a WE 32100 Microprocessor based single-board microcomputer evaluation system. It can be used as a prototyping system to evaluate the performance and the hardware/software capabilities of the WE 32100 Microprocessor in an application environment.

The evaluation board contains a *WE* 32100 Microprocessor operating at 18 MHz, an 18-MHz *WE* 32102 Clock, a *WE* 32101 Memory Management Unit, and a *WE* 32106 Math Acceleration Unit. Also included are a ROMresident monitor program, 96 Kbytes of RAM, address decoding, RS-232C serial I/O ports, programmable parallel I/O lines, programmable interval timers, and an interrupt controller.

### **Board-Level Products**

The WE 321SB VMEbus Single Board Computer (SBC) is a 32-bit single-board computer that enables the rapid development of VMEbus systems for applications that require the highest level of performance, either in a UNIX System or other operating system environment.

The SBC is provided in a double-height Eurocard format and interfaces with VMEbus peripheral boards through the Rev. C.1 VMEbus interface. Included with the SBC are the *WE* 32100 Microprocessor, *WE* 32101 Memory Management Unit, and *WE* 32106 Math Acceleration Unit, 1 Mbyte of DRAM, EPROM/ROM configured up to 256 Kbytes, two serial ports, three timer/counters, and interrupt circuitry. The SBC can also be configured to operate with UNIX System V/VME Release 2.1 or 3.1 Software.

### **Development Software**

The WE 321SG C-Software Generation Programs (C-SGP) are a collection of support software tools that allow the use of the computing power of a host UNIX System to aid in the creation and debugging of software for the WE 32100 Microprocessor chip set.

The C-SGP products satisfy two user programming environments:

- Native Environment the WE 321SG C-Software Generation Programs (native C-SGP) for systems on which the host is the target system and the host/target system is running the UNIX Operating System

- Cross Environment the WE 321SG Cross C-Software Generation Programs (Cross C-SGP) for systems on which the host is running the UNIX Operating System, and the target contains the UNIX Operating System, an operating system other than the UNIX Operating System, or is embedded in an environment with no operating system.

Each of the user programming environments can be configured in either of two floating-point modes: math acceleration unit (**MAU**) or floating-point emulation (**FPE**). The **MAU** mode provides enhanced floating-point performance through the use of in-line compilation of the MAU instruction set (MIS) for the WE 32106 Math Acceleration Unit. Alternatively, the FPE mode provides the flexibility of supporting target systems with or without a math acceleration unit. The FPE mode compiles floating-point operations as calls to library routines that either execute MIS or emulate the operations, depending on whether a math acceleration unit has been determined to be present at process start-up. For the Cross C-SGP, the FPE mode assumes the target system does not have a math acceleration unit. This support software provides utility programs that enable the user to write applications software in C language or assembly language, and then translate it into machine code.

# **Operating System Software**

UNIX System V is a multi-user operating system whose modular design simplifies the manipulation of files and commands. The hierarchical file structure allows for easy adding, deleting, and moving of files within a structure set up by the user. Input to commands can come from a terminal or a file, and output can be directed to files or to peripheral devices. The output of a command can be directed to the input of another command, allowing users to easily create specialized functions.

The UNIX System shell is also a programming language that can be used to create user definable applications and functions.

The UNIX System oversees the execution of many user programs and commands. Although these programs and commands seem to execute simultaneously, each application is scheduled to use the processor for a short period of time to the exclusion of all other programs. Thus, in addition to providing a multi-user system, the UNIX System affords each user the capability of running several programs at once. This feature is called multiprogramming. Many UNIX System based products are available from AT&T and other vendors. Descriptions of these products can be found in the AT&T Computer Software Catalog. Products offered through the AT&T UNIX System Toolchest are available to customers who have a UNIX System source license.

# **Quality Control and Reliability**

AT&T standards and stringent processing controls, along with the design and construction techniques developed at AT&T Bell Laboratories, ensure the excellent quality and reliability of AT&T devices. Laboratory tests and field failure data confirm that high quality, reliable products are produced at the component, circuit pack/board, and system levels. Devices are tested by a comparison of the actual electrical, mechanical, or visual properties of the device against what is specified to the user or what is specified as a manufacturing requirement. Quality is determined at a single point in time, reliability is ascertained over a longer period of time.

# **Quality Control**

The engineering Quality Control (QC) and Final Inspection (FI) organizations located at each integrated circuit (IC) manufacturing plant perform the actual inspection and testing of devices. After the products have been inspected, the resident Quality Assurance (QA) organizations audit the results of the tests to determine acceptability. Quality is usually stated in terms of the number of defects contained in an IC population.

Various mechanical tests are performed to ensure the integrity of internal lead bonds and the strength of exterior leads. Packages are visually inspected during assembly to check for defects such as poor alignment of bonds or damaged wires that could be a reliability risk. Assembly shop tests are then repeated by QA and FI on a sample of devices prior to shipment. Tests performed include worst-case conditions, speed, leakage, power supply current, etc. The tests are usually performed at room temperature and/or elevated temperature.

Operational life testing (OLT) is a method of testing for reliability using simulated worst-case field conditions. Mechanical and électrical stress conditions beyond normal specifications are applied to accelerate latent manufacturing defects. Effective screens for mechanical problems are thermal cycling and hot testing, since some mechanical defects are only minimally affected by accelerated stress conditions.

Board-level products are given visual inspections during and after each phase of

assembly. Upon completion of assembly, the boards are subjected to computer controlled testing, checking for manufacturing defects, opens, shorts, resistance values, and in some cases, capacitance values. Next, a burn-in procedure is performed, simulating 100 days of operation under accelerated temperatures and other stressful conditions. This test is used to detect early defects. The boards are then subjected to a rigorous functional test, emulating actual operating environments. During this test, more board options are selected than would be normally used by a customer. Finally, another inspection and further testing is performed by an independent Quality Assurance team.

### Reliability

In order to provide a comprehensive measure of product reliability, a two-tier program of stressing is used.

**Level 1.** Level 1 is the extended life testing program in which a sample of 100 devices is taken once every six weeks from each reliability testing group and stressed for periods simulating 40 years of product life. The length of stressing time depends on the acceleration factors determined for the individual tests.

Level 2. Level 2 is the normal monitoring program in which a sample of 100 devices is chosen from each testing group every week and stressed for a period approximating 10 years of product life.

To facilitate product sampling and ensure complete coverage of the reliability program, all products are grouped into families according to their basic design and function, such as custom logic, memories, microprocessors, codec/analog and digital signal processors. The families are further divided into test groups for sample selection testing. Test groups are based on factors most likely affected by the tests being performed. An explanation of each test is given below.

#### High Temperature Operating Bias/High Temperature High Bias (HTOB/HTHB)

The HTOB/HTHB testing accelerates failure mechanisms that are thermally excited by high temperatures, such as ionic drift, electrothermal migration, oxide breakdown, silicon material

4 4

defects, and assembly-related mechanisms. Another concern is the interaction between packaging materials and silicon processing. Therefore, reliability test groupings for HTOB/HTHB are based on silicon processing, design rules, silicon fabrication facilities and packaging lines.

HTOB/HTHB is performed at the following temperatures and times:

|       | Level 1  | Level 2 | Accel.<br>Factor |

|-------|----------|---------|------------------|

| 125 ℃ | 2350 hrs | 700 hrs | 128              |

| 135 ℃ | 1260     | 385     | 238              |

| 150 ℃ | 525      | 160     | 570              |

#### Temperature Humidity Bias (THB)

THB tests the effectiveness of chip passivation and device packaging. High humidities in the presence of electrical bias promotes electrochemical corrosion, electrothermal migration and other chemical reactions involving the presence of water. Test groupings for THB are based on packaging materials, package types and packaging lines. The test conditions for this test are 85°C and 85% relative humidity (85/85).

Two options are available for stressing parts for THB. They are:

**Option 1.** Devices are soaked in the 85/85 chamber with no bias for 48 hours, after which time the bias is applied and the parts are stressed for 240 hours for level 2 conditions and 800 hours for level 1 conditions.

**Option 2.** Devices are placed in a steam bomb at 121 °C/15 psig with no bias for 96 hours after which they are placed in the 85/85 chamber with bias applied for 48 hours for level 2 conditions and 160 hours for level 1 conditions. The steam bomb increases acceleration by a factor of 5.

#### **Temperature Cycling (TC)**

TC applies thermally-induced stress to the devices to accelerate material fatigue and precipitate failures associated with thermal expansion mismatches. TC groupings are based on packaging materials, package types, and packaging lines.

Devices are stressed from -40 °C to +130 °C with no bias applied. The level 2 stressing duration is 60 cycles; the level 1 stressing duration is 180 cycles.

# Handling

AT&T products have long life expectancy with a corresponding low failure rate when handling and operating specifications are followed by the user. Operating specifications include product mounting, use, operating limits, power requirements, environmental conditions, and other items specific to the product.

### **Integrated Circuits**

Observe the following instructions when handling and using integrated circuits.

Precaution against static discharge must be observed always. This includes grounding all personnel and equipment before contact with static-sensitive devices.

In assembly, the device solder bath (fountain) temperature should not exceed 300 °C for a maximum bath time limited to 10 seconds. For installation with a soldering iron, the iron temperature (tip) should not exceed 500 °C, and solder time per lead should be limited to 5 seconds.

Following completion of assembly and soldering operations, all printed wiring assemblies should be cleaned to remove fingerprints, dust, dirt, grease, excessive flux residue, and other foreign matter. A brush cleaning process using solvents is the acceptable cleaning method, provided only occasional isolated droplets of solvent come in contact with the devices and the component side of the board. The recommended solvents are chlorinated hydrocarbons such as trichlorethylene, 1,1,1-trichloroethane, and perchloroethylene.

# **Board-Level Products**

Observe these precautions when unpacking and handling board level products:

- Ground yourself before handling; circuit boards contain static-sensitive devices

- Avoid touching areas of integrated circuits; static discharge can damage these circuits

- Store boards in conductive bags when not in use.

#### Assistance

#### Diskettes

4 0

The following guidelines should be observed in order to protect the data stored on diskettes:

- Store diskettes vertically in their protective sleeves

- Protect diskettes from direct sunlight

- Storage and operating temperature ranges for diskettes are 50 °F—125 °F (10 °C—50 °C)

- Always handle a diskette by the sleeve; never touch exposed surfaces

- Never bend or fold diskettes

- Do not use or store diskettes near magnets or other sources of magnetic fields

- Use only felt-tipped pens when writing on diskettes

- Exercise caution when inserting diskettes into diskette drives.

### Military Specification Devices

AT&T will offer military versions of its *WE* 32100 Microprocessors and Peripherals. The devices will meet military standards 883 and possibly the Joint Army-Navy (JAN) qualification. Initial production of the CPU, MMU, and MAU will be set at 10 MHz in the second half of 1988. The DRAM controller, the DMA controller, and 14-MHz CPU, MMU, and MAU are scheduled to be offered in 1989. Future plans include offerings of military versions of the *WE* 32200 Microprocessors and Peripherals.

### Assistance

This data book contains technical information on the WE 32-Bit Microprocessors, peripherals, and hardware and software support systems.

Additional information is available in the form of manuals, application notes, and documentation from the UNIX Operating System.

For details concerning warranty, repairs, or ordering or to obtain additional information, contact your AT&T Account Manager or call:

- AT&T Technologies

Dept. 51AL603140

555 Union Boulevard

Allentown, PA 18103

1-800-372-2447

- AT&T Microelectronics Freischützstrasse 92 8000 Munich 81 West Germany Tel. 0 89/95 97 0 Telex 5 216 884

- AT&T Microlelectronics Pte. Ltd. 745 Larong 5 Toa Payoh Singapore 1231 Tel. 250 8422/253 3722 Telex RS 21473/RS 55038

- AT&T International Japan Ltd. Nippon Press Center Bldg.

2-1, Uchisaiwai-cho, 2-Chome, Chiyoda-ku, Tokyo 100 Japan Tel. (03) 593 3301 Telex J32562 ATTIJ

# Warranties

Contracts of sale for the items described in this Data Book will include the following warranty language.

#### **Device Warranty**

Seller warrants to buyer that products of its manufacture will be, on the date of shipment of the product, free from defects in material and workmanship and will conform to Seller's written specifications provided to Buyer or to the specifications, if any, identified in an order and accepted by Seller, other than specifications specifying performance for a period of time. If any defect in material or workmanship or failure to meet said published specifications (a "defect") appears in the product, Seller will, at its option, either repair or replace the defective product without charge at Seller's manufacturing or repair facility or credit or refund the purchase price of the defective product, [ii] Buyer notifies Seller in writing of the claimed defect no later than thirty (30) days after the end of the twelve (12) month period, and [iii] Seller's examination of the product discloses that the claimed defect actually exists.

Buyer shall follow Seller's instructions regarding return of defective product, and no product will be accepted for repair, replacement, credit, or refund without the written authorization of and in accordance with Seller's instructions. In the case of any such return, Buyer shall bear the risk of loss or damage and shall prepay all transportation chargers to Seller. Repaired or replacement product will be shipped, freight prepaid by Seller, and Buyer shall bear the risk of loss or damage. The replaced product shall become Seller's property. In no event shall Seller be responsible for destination or reinstallation of the product or for the expenses thereof. If Seller determines that the products are not defective, Buyer shall pay Seller all costs of handling, inspection, repairs, and transportation at Seller's then prevailing rates.

Repairs and replacements covered by the above warranty are warranted to be free from defects as set forth above except that the defect must appear [i] with three (3) months from the date of repair or replacement or [ii] prior to the expiration of the above twelve (12) month period, whichever is later.

With respect to products not manufactured by Seller, Seller, to the extent permitted, extends the warranties and affords the remedies to Buyer given to Seller by its vendor of said products.

The foregoing warranties do not extend [a] to expendable items or [b] to experimental or developmental products or [c] to products which have [i] been subject to misuse, neglect, accident or abuse; [ii] been wired, repaired or altered by anyone other than Seller; [iii] been used in material violation of Seller's instructions, or [iv] have had their serial numbers or month and year of manufacture or shipment removed, defaced, or altered. The term "software" means a set of logical instructions and tables of information which guide the functioning of a processor. Such set may be contained in any medium whatsoever, including without limitation hardware containing a pattern of bits representing such set provided, however, the term "software" does not mean or include the medium.

THE FOREGOING WARRANTIES ARE IN LIEU AND EXCLUDE ALL OTHER EXPRESS AND IMPLIED WARRANTIES, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. BUYER'S SOLE AND EXCLUSIVE REMEDY SHALL BE SELLER'S OBLIGATION TO REPAIR OR REPLACE OR CREDIT OR REFUND AS SET FORTH ABOVE.

#### Warranties

# Hardware Warranty for WE<sup>®</sup> 321EB Microprocessor Evaluation Board, WE<sup>®</sup> 321DS Microprocessor Development System, WE<sup>®</sup> 321DM CPU & MMU Device Monitor, WE<sup>®</sup> 322DM CPU & MMU Device Monitor

Seller warrants to Buyer that Hardware Products will, at the time of shipment and under proper and normal use, be free from defects in material or workmanship and will conform to Seller's applicable descriptions. If any failure to conform to this WARRANTY appears in any Hardware Product, Seller will, at its option, either repair or replace the defective Product without charge at Seller's manufacturing or repair facility or at Buyer's facility, or will refund the purchase price of the defective Hardware Product, PROVIDED: that Buyer notifies Seller of the purported failure to conform to this WARRANTY within ninety (90) days after the date of shipment of the Hardware Product to Buyer and that Seller's examination of the Hardware Product discloses that the purported failure to conform to this WARRANTY is present. Buyer shall follow Seller's instructions regarding return of Hardware Products, and no Hardware Product will be accepted for repair, replacement or refund absent Buyer's following such instructions. In the case of any such return, Buyer shall bear the risk of loss or damage and shall prepay all transportation charges to Seller. Repaired or replacement Hardware Products shall be shipped to a continental U.S. destination by Seller at its expense and risk of loss or damage. Buyer shall be responsible for any customs duties, local taxes and expenses related to the importation of repair or replacement Hardware Products and any requested premium transportation. Replaced parts shall become Seller's property. Seller shall not be responsible under this WARRANTY for deinstallation or reinstallation or for related expenses arising out of the alteration of Buyer's or a third party's premises or building or removal, replacement or relocation of other items not purchased hereunder. If Seller determines that the Hardware Products do not fail to conform to this WARRANTY, Buyer shall pay Seller all costs of handling, inspection, repairs and transportation at Seller's then prevailing rates.

Repaired and replaced parts provided under the above WARRANTY are warranted as set forth above, but only for sixty (60) days from the date of repair or replacement, or, for the remainder of the WARRANTY period, whichever is greater.

The foregoing WARRANTY does not extend to Software Products; to expendable items; to experimental or developmental Hardware Products; or to Hardware Products which have been subject to misuse, neglect, accident or abuse; have been improperly wired, repaired or altered by anyone other than Seller, have been improperly installed, stored or maintained by anyone other than Seller, have been used in material violation of Seller's instructions; or have had their serial numbers or month and year of manufacture or shipment removed, defaced or altered.

THE FOREGOING WARRANTY IS IN LIEU OF AND EXCLUDES ALL OTHER EXPRESSED AND IMPLIED WARRANTIES, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. BUYER'S SOLE AND EXCLUSIVE REMEDY SHALL BE SELLER'S OBLIGATION TO REPAIR, REPLACE OR REFUND AS SET FORTH ABOVE.

# Hardware Warranty for WE 321SB VMEbus Single Board Computer

Seller warrants to Buyer that Hardware Products will, at the time of shipment and under proper and normal use, be free from defects in material or workmanship and will conform to Seller's applicable descriptions. If any failure to conform to this WARRANTY appears in any Hardware Product, Seller will, at its option, either repair or replace the defective Product without charge at Seller's manufacturing or repair facility or at Buyer's facility, or will refund the purchase price of the defective Hardware Product, PROVIDED: that Buyer notifies Seller of the purported failure to conform to this WARRANTY within ninety (90) days after the date of shipment of the Hardware Product to Buyer and that Seller's examination of the Hardware Product discloses that the purported failure to conform to this WARRANTY is present. Buyer shall follow Seller's instructions regarding return of Hardware Products, and no Hardware Product will be accepted for repair, replacement or refund absent Buyer's following such instructions. In the case of any such return, Buyer shall bear the risk of loss or damage and shall prepay all transportation charges to Seller. Repaired or replacement Hardware Products shall be shipped to a continental U.S. destination by Seller at its expense and risk of loss or damage. Buyer shall be responsible for any customs duties, local taxes and expenses related to the importation of repair or replacement Hardware Products and any requested premium transportation. Replaced parts shall become Seller's property. Seller shall not be responsible under this WARRANTY for deinstallation or reinstallation or for related expenses arising out of the alteration of Buyer's or a third party's premises or building or removal, replacement or relocation of other items not purchased hereunder. If Seller determines that the Hardware Products do not fail to conform to this WARRANTY, Buyer shall pay Seller all costs of handling, inspection, repairs and transportation at Seller's then prevailing rates.

Repaired and replaced parts provided under the above WARRANTY are warranted as set forth above, but only for thirty (30) days from the date of repair or replacement, or, for the remainder of the WARRANTY period, whichever is greater.

The foregoing WARRANTY does not extend to Software Products; to expendable items; to experimental or developmental Hardware Products; or to Hardware Products which have been subject to misuse, neglect, accident or abuse; have been improperly wired, repaired or altered by anyone other than Seller, have been improperly installed, stored or maintained by anyone other than Seller, have been used in material violation of Seller's instructions; or have had their serial numbers or month and year of manufacture or shipment removed, defaced or altered.

THE FOREGOING WARRANTY IS IN LIEU OF AND EXCLUDES ALL OTHER EXPRESSED AND IMPLIED WARRANTIES, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. BUYER'S SOLE AND EXCLUSIVE REMEDY SHALL BE SELLER'S OBLIGATION TO REPAIR, REPLACE OR REFUND AS SET FORTH ABOVE.

#### Warranties

#### Software Product Warranty

Seller warrants to Buyer that, upon shipment, Software Products will be free from defects which result in a material failure of the applicable Hardware Product to execute instructions.

If, under normal and proper licensed use, the Software Products prove to have such a defect and Buyer notifies Seller of such defect within ninety (90) days from the date of shipment thereof, Seller, at its option, will either correct or replace the same without charge at its facility or provide a refund or credit. No Software Product will be accepted for correction or replacement except upon the written authorization and in accordance with instructions of Seller. Any transportation expenses associated with returning such Software Product to Seller shall be borne by Buyer. Seller shall pay the costs of transportation of the correction may be incorporated into a new release of the Software Product which will be made available to Buyer or such corrections may be performed at Buyer's facility.

In the event that Seller determines after investigation that the Software Products are not defective, Buyer shall pay all costs of handling, inspection, testing and transportation, including travel and subsistence costs incurred by Seller's personnel.

Seller makes no warranty as to the following: defects other than those which result in a material failure of the applicable Hardware Product to execute instructions; defects related to Buyer's misuse, neglect, accident or abuse; defects related to Buyer's alteration of software; defects appearing in software used in violation of the license granted hereby that Software Products will meet the requirements of Buyer or that the operation of the Hardware Products using the Software Products will be uninterrupted or error-free.

THE FOREGOING WARRANTY IS EXCLUSIVE AND IS IN LIEU OF ALL OTHER EXPRESSED AND IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, WARRANTIES OR MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. BUYER'S SOLE AND EXCLUSIVE REMEDY SHALL BE SELLER'S OBLIGATION TO CORRECT, REPLACE, CREDIT OR REFUND, AS SET FORTH ABOVE.

# WE<sup>®</sup> 32100 Microprocessor

### Description

The WE 32100 Microprocessor (CPU) is a highperformance, single-chip, 32-bit central processing unit designed for efficient operation in a high-level language environment. It performs all the system address generation, control, memory access, and processing functions required in a 32-bit microcomputer system. It has separate 32-bit address and data buses. System memory is addressed over the 32-bit address bus by using either physical or virtual addresses. Data is read or written over the 32-bit bidirectional data bus in word (32-bit), halfword (16-bit), or byte (8-bit) widths. Extensive addressing modes result in a symmetric, versatile, and powerful instruction set. The WE 32100 Microprocessor is available in 10-, 14-, and 18-MHz versions; requires a single 5 V supply; and is available in a 125-pin square, ceramic pin grid array (PGA) package.

# Features

- Powerful and versatile instruction set

- On-chip instruction cache

- 4 Gbytes (2<sup>32</sup>) of direct memory addressing

- Physical and virtual addressing

- Coprocessor interface

- DMA and multiprocessor environment support

- 15 levels of interrupts

- Autovector and nonmaskable interrupt facilities

- Four levels of execution privilege: kernel, executive, supervisor, and user

- Synchronous or asynchronous interfacing to external devices

- Nine 32-bit general-purpose registers

- Seven 32-bit special-purpose registers

- Memory-mapped I/O

- Complete floating-point support via the WE 32106 Math Acceleration Unit

### WE® 32100 Microprocessor

| Description                             | 1  |

|-----------------------------------------|----|

| Features                                | 1  |

| User Information                        | 3  |

| Architectural Summary                   | 3  |

| Process Status Word                     | 4  |

| Process Control Block                   | 6  |

| Interrupts                              | 6  |

| Bus Arbitration                         | 10 |

| Direct Memory Access and Multiprocessor | •  |

| Support                                 | 10 |

| Coprocessor Interface                   | 10 |

| Read-Interlocked Operation              | 10 |

| Reset                                   | 10 |

| Flags/Conditions                        | 11 |

| Instruction Set and Summaries by        |    |

| Mnemonic and Opcode                     | 12 |

| Instruction Set Summary by Functional   |    |

| Group                                   | 21 |

| Instruction Timing                      | 21 |

| Arithmetic Group                        | 21 |

| Data Transfer Group                     | 23 |

| Logical Group                           | 24 |

| Program Control Group                   | 25 |

| Stack and Miscellaneous Groups    | 27 |

|-----------------------------------|----|

| Coprocessor Group Instruction     | 28 |

| Operating System Instructions and |    |

| Microsequences                    | 28 |

| Other Microsequences              | 28 |

| Addressing Modes                  | 30 |

| Exceptions                        | 33 |

| Bus Exceptions                    | 33 |

| Exceptional Conditions            | 33 |

| Normal Exceptions                 | 33 |

| Stack Exceptions                  | 35 |

| Process Exceptions                | 35 |

| Reset Exceptions                  | 35 |

| Pin Descriptions                  | 35 |

| Numerical Order                   | 36 |

| Functional Groups                 | 39 |

| Characteristics                   | 45 |

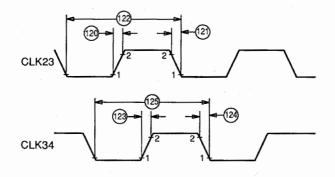

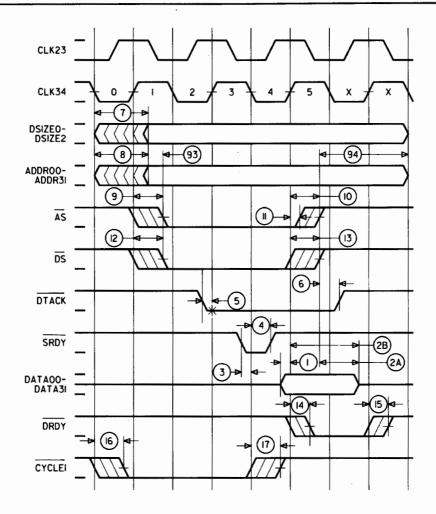

| Timing Characteristics            | 45 |

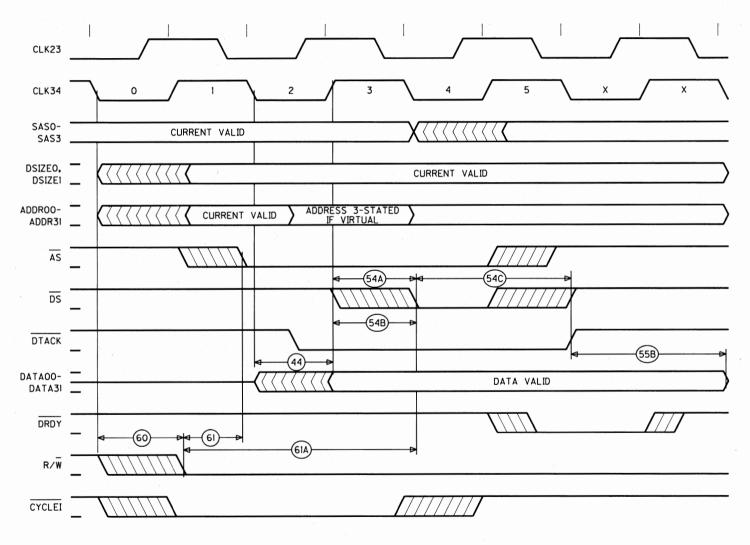

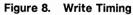

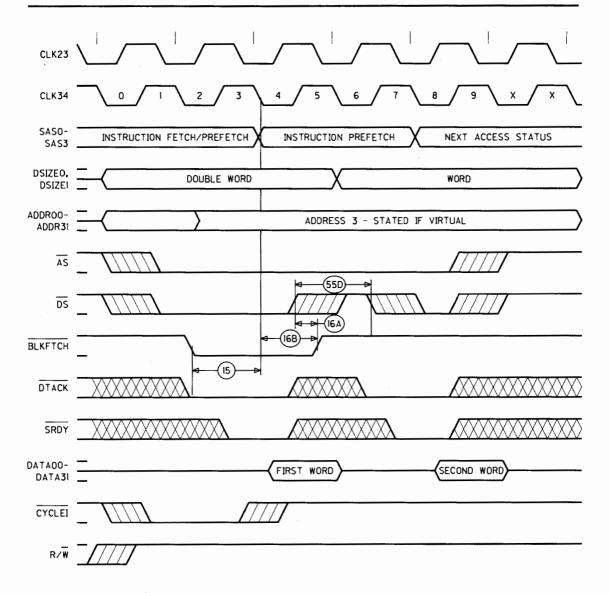

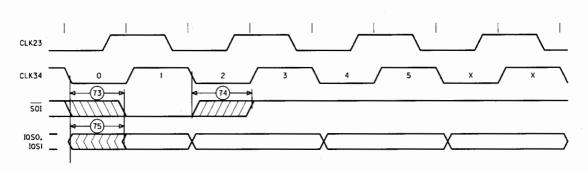

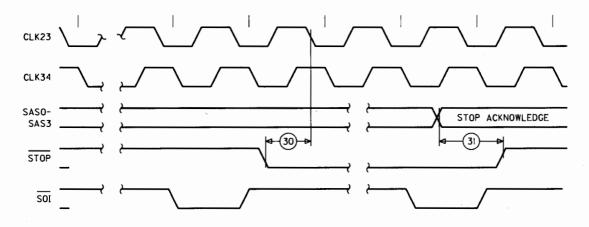

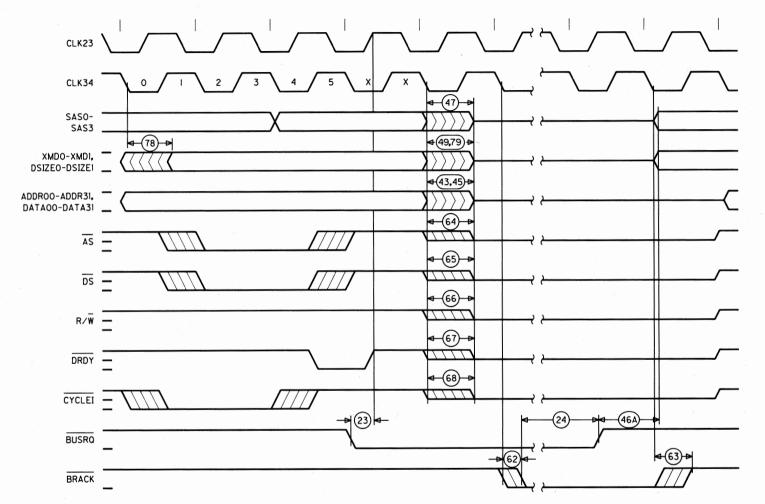

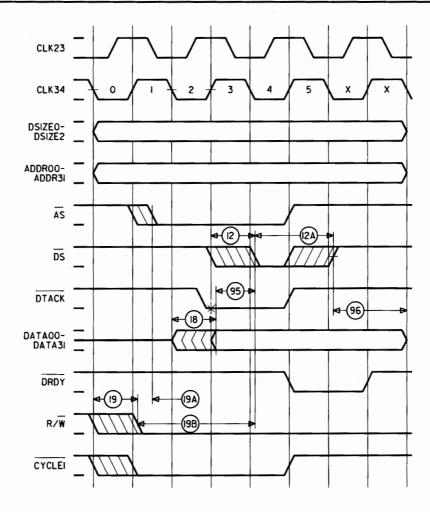

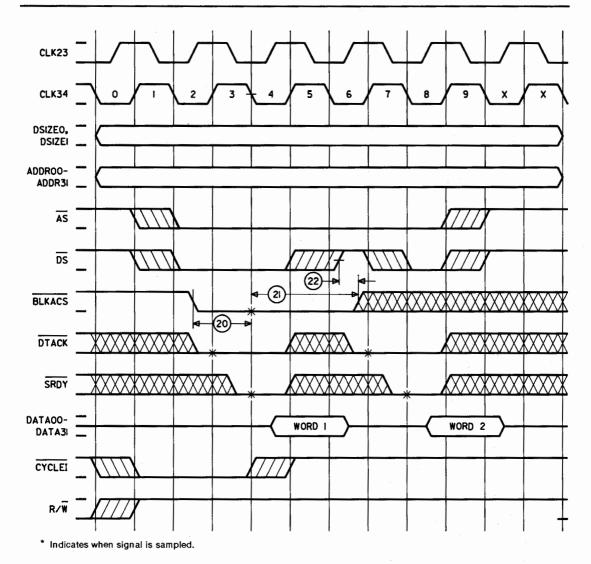

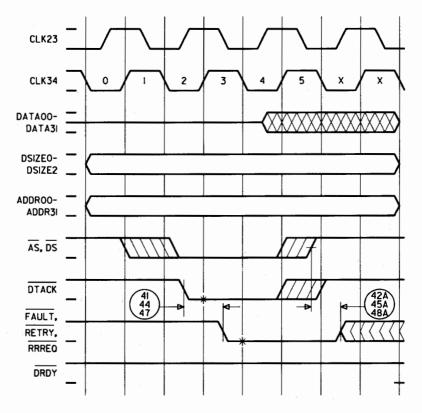

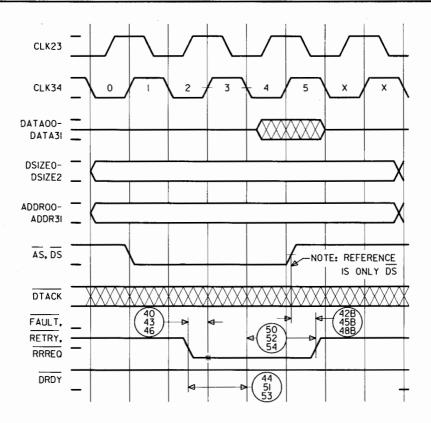

| Timing Diagrams                   | 49 |

| Electrical Characteristics        | 62 |

| Inputs                            | 62 |

| Outputs                           | 62 |

| Operating Conditions              | 63 |

|                                   |    |

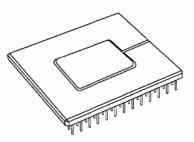

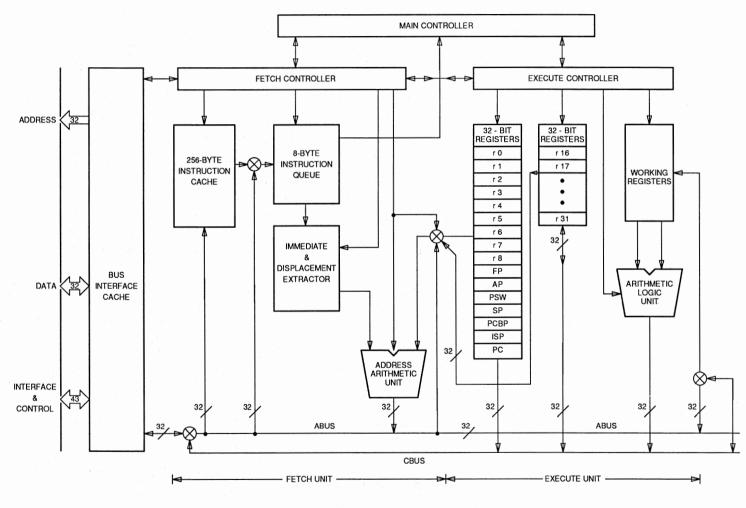

Figure 1. WE® 32100 Microprocessor Block Diagram

# **User Information**

# Architectural Summary

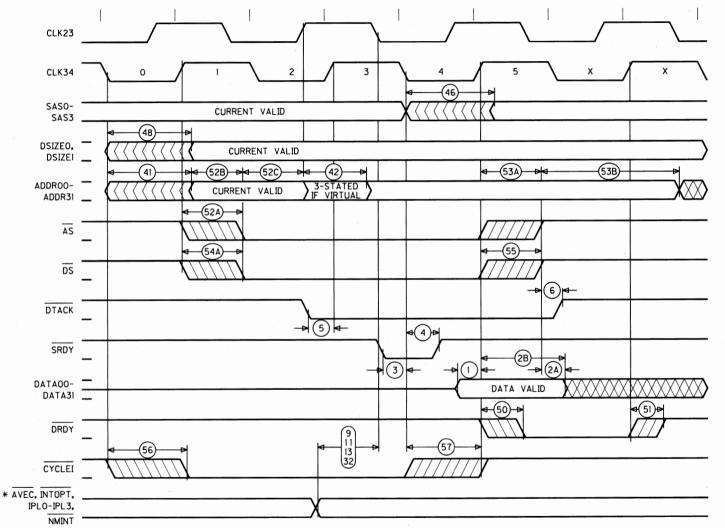

The WE 32100 Microprocessor provides separate 32-bit address and data buses to the external system, eliminating the need for external multiplexing/demultiplexing. The memory or peripherals mapped into the system memory are addressed over the 32-bit address bus by using either physical or virtual addresses. Data is read to or written from the microprocessor over the 32-bit bidirectional data bus in word (32-bit), halfword (16-bit), or byte (8-bit) widths. The microprocessor automatically extends bytes and halfwords to 32 bits for processing.

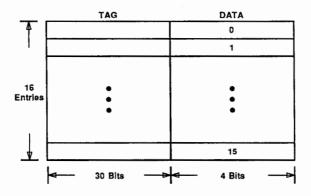

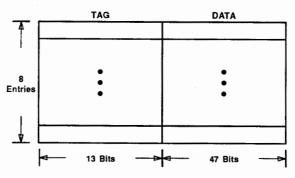

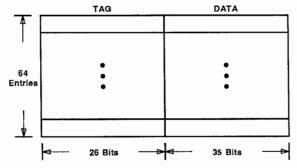

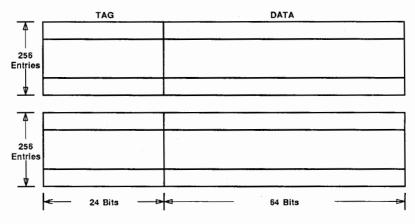

Execution speed is enhanced by an internal instruction queue and an internal instruction cache. The instruction queue is an 8-byte firstin-first-out (FIFO) queue that stores prefetched instructions. The queue is used to pipeline instructions, thereby enabling the microprocessor to overlap the execution of instructions while tracking each separately. The instruction cache is a 64-word on-chip cache used to increase the microprocessor's performance by reducing external memory reads for instruction fetches. When an instruction fetch from memory occurs, instruction data is placed in both the instruction queue and the instruction cache. If that instruction data is needed again, it is fetched from the cache rather than from external memory, resulting in increased performance.

The microprocessor uses address and data strobes, as well as other interface and control signals, to control information flow over the system address and data buses. These signals provide timing for the latching of information and facilitate interfacing with commercial memories and peripherals. The microprocessor also accommodates wait-state generation to allow hand-shaking with slow peripherals.

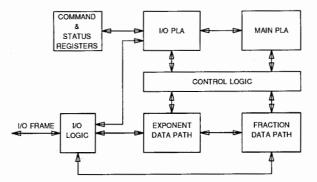

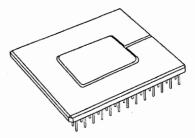

Figure 1 shows the four major sections of the *WE* 32100 Microprocessor: bus interface control, main controller, fetch unit, and execute unit.

**Bus Interface Control.** Provides all the strobes and control signals necessary to implement the interface with peripherals.

Main Controller. Responsible for acquiring and decoding instruction opcodes and for directing

the action of the fetch and execute controllers as the specified instruction is executed. The main controller also responds to and directs the handling of interrupts and exceptional conditions.

**Fetch Unit.** Handles the instruction stream and performs memory-based operand accesses. It consists of a fetch controller, an instruction cache, an instruction queue, an immediate and displacement extractor, and an address arithmetic unit (AAU).

Execute Unit. Performs all arithmetic and logical operations and all shift and rotate operations and computes condition flags. It consists of an execute controller, sixteen 32-bit registers, working registers, and a 33-bit-wide arithmetic logic unit (ALU). The sixteen 32-bit registers are user-accessible and include nine general-purpose registers (r0-r8) and seven dedicated registers (r9-r15). All of the registers except the program counter (r15) can be referenced in all addressing modes. The processor status word (r11), process control block pointer (r13), and interrupt stack pointer (r14) are privileged registers that can be read at any time, but can be written only when the microprocessor is in the kernel (highest) execution level. The working registers are used exclusively by the microprocessor and are not user-accessible.

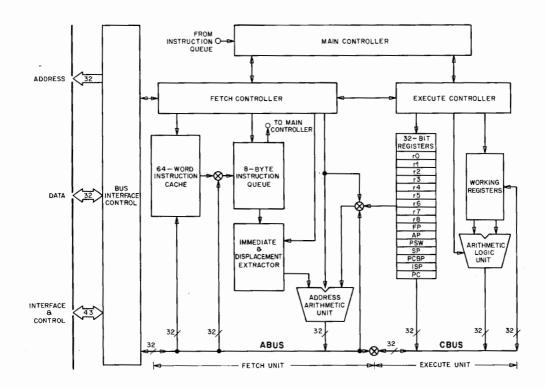

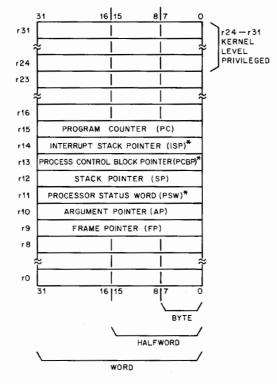

The sixteen 32-bit registers, defined below, are shown on Figure 2.

**r0—r8** – **General-Purpose Registers.** These nine 32-bit registers can be used for accumulation, addressing, or temporary data storage. They can be used in any addressing mode by any program – privileged or nonprivileged. Registers r0, r1, and r2 are also implicitly used by certain data transfer and operating system instructions.

**r9** – **Frame Pointer (FP).** Points to the beginning location in the stack of a function's local variables.

**r10** – **Argument Pointer (AP).** Points to the beginning location in the stack to which a set of arguments for a function have been pushed.

r11 – Processor Status Word (PSW). Contains information that determines the current execution state. This information includes current exception type; an internal state code; the current interrupt priority level; trace enable, trace mask, cache disable, cache flush disable,

#### WE<sup>®</sup> 32100 Microprocessor

\* Kernel-level privileged.

#### Figure 2. CPU Registers

quick-interrupt enable, and enable overflow trap flags; previous and current execution levels; and four condition codes that indicate zero (Z), overflow (V), negative (N), and carry (C). The PSW is kernel-level privileged.

r12 – Stack Pointer (SP). Contains the current 32-bit address of the top of the execution stack, i.e., the memory address of the next place in which an item can be stored (pushed) on the stack or of the last place from which an item was retrieved (popped) from the stack. The stack pointer implements a last-in-first-out (LIFO) queue, which supports efficient subroutine linkage and local variable storage.

r13 – Process Control Block Pointer (PCBP). Contains the 32-bit address of the process control block (PCB) for the current process. The PCBP is kernel-level privileged.

r14 – Interrupt Stack Pointer (ISP). Contains the 32-bit memory address of the top of the interrupt stack. This stack is used when an interrupt request is received and when the call process (CALLPS) and return to process (RETPS) instructions are encountered. The ISP is kernel-level privileged.

r15 – Program Counter (PC). Contains the 32bit memory address of the instruction being executed or, upon instruction completion, the starting address of the next instruction to be executed.

#### Processor Status Word (PSW)

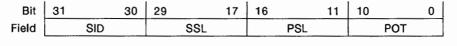

The PSW (r11) contains several state variables associated with the current process and provides a means of determining the microprocessor's execution state at any time. The word format for the PSW is shown on Figure 3.

The following define the PSW bit field.

Bits 0, 1 – Exception Type (ET). Bits 0 and 1 represent exceptions generated during operations. This read-only field is interpreted as:

| Bit 1 | Bit 0 | Description          |

|-------|-------|----------------------|

| 0     | 0     | On reset exception   |

| 0     | 1     | On process exception |

| 1     | 0     | On stack exception   |

| 1     | 1     | On normal exception  |

Bit 2 – Trace Mask (TM). Bit 2 enables the masking of a trace trap. This read-only field masks the trace enable (TE) bit for the duration of one instruction in order to avoid a trace trap. The TM bit is set (1) at the beginning of every instruction and cleared (0) as part of each microsequence (see Microsequences) that performs a context switch or a return from gate (RETG), or when any fault or interrupt is detected and responded to.

Bits 3 through 6 – Internal State Code (ISC). Bits 3 through 6 represent the microprocessor internal state code and distinguish between exceptions of the same exception type. This field is used in conjunction with the exception type (ET) field to determine which type of exception occurred. Normal exceptional conditions are decoded on a priority scheme if more than one occurs in a particular cycle. Table 1 lists the ISC values.

|       |     |      |     |     |    |    | 21 18 |    |     |    |    |   |   |     |    |    |

|-------|-----|------|-----|-----|----|----|-------|----|-----|----|----|---|---|-----|----|----|

| Field | ปทเ | used | CFD | QIE | CD | QE | NZVC  | TE | IPL | СМ | PM | R | 1 | ISC | тм | ET |

Figure 3. Word Format for the PSW

Bits 7, 8 – Register-Initial Context (RI). Bits 7 and 8 control the microprocessor context switching strategy. The I bit (bit 7) determines if a process executes from an initial (I=1) or an intermediate saved context. The R bit (bit 8, read only) determines if the registers of a process should be saved during a process switch (saved if R=1; not saved if R=0). It also controls block moves, which can be used to change MMU information.

#### Table 1. Exceptional Conditions

| Exception<br>Type                 | Exception                                                                                                     | Internal<br>State<br>Code Bit<br>6 5 4 3                                                                                                |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Normal<br>exception<br>(ET = 11)  | Integer zero-divide<br>Trace trap<br>Illegal opcode<br>Reserved opcode                                        | 0 0 0 0*<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1                                                                                               |

|                                   | Invalid descriptor<br>External memory fault<br>Gate vector fault<br>Illegal level change                      | 0 1 0 0*<br>0 1 0 1<br>0 1 1 0<br>0 1 1 1                                                                                               |

|                                   | Reserved data type<br>Integer overflow<br>Privileged opcode<br>Breakpoint trap<br>Privileged register         | 1 0 0 0*<br>1 0 0 1<br>1 0 1 0<br>1 1 1 0<br>1 1 1 1                                                                                    |

| Stack<br>exception<br>(ET = 10)   | Stack bound<br>Stack fault<br>Interrupt ID fetch                                                              | 0 0 0 0<br>0 0 0 1<br>0 0 1 1                                                                                                           |

| Process<br>exception<br>(ET = 01) | Old PCB fault<br>Gate PCB fault<br>New PCB fault                                                              | 0 0 0 0<br>0 0 0 1<br>0 1 0 0                                                                                                           |

| Reset<br>exception<br>(ET = 00)   | Old PCB fault<br>System data<br>Interrupt stack fault<br>External reset<br>New PCB fault<br>Gate vector fault | $\begin{array}{ccccccc} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 \end{array}$ |

Exceptional conditions that reset the PSW flags.

#### Bits 9, 10 – Previous Execution Level (PM).

Bits 9 and 10 represent the previous execution level and are interpreted as:

| Bit 10 | Bit 9 | Description      |

|--------|-------|------------------|

| 0      | 0     | Kernel level     |

| 0      | 1     | Executive level  |

| 1      | 0     | Supervisor level |

| 1      | 1     | User level       |

|        |       |                  |

#### Bits 11, 12 - Current Execution Level (CM).

Bits 11 and 12 represent the current execution level. The code of bits 11 and 12 is interpreted in the same manner as that of bits 9 and 10 (respectively) in the PM code.

Changes to the CM field via instructions that have the PSW as an explicit destination may affect the XMD pins during a prefetch access. Accordingly, only microsequence instructions should be used to change the CM field state.

Bits 13 through 16 – Interrupt Priority Level (IPL). Bits 13 through 16 represent the current interrupt priority level. Fifteen levels of interrupts are available. An interrupt, unless it is a nonmaskable interrupt, must have a higher priority level than the current IPL of the PSW in order to be acknowledged. Level 0000 indicates that any of the fifteen interrupt priority levels (0001 through 1111) can interrupt the microprocessor, while level 1111 indicates that no interrupt the microprocessor since 1111 is the highest interrupt priority level.

**Bit 17 – Trace Enable (TE).** Bit 17 enables the trace function. When set (1), it causes a trace trap to occur after execution of the next instruction. Debugging and analysis software use this facility for single-stepping a program. Changes to the TE field via instructions that have the PSW as an explicit destination may cause unpredictable trace-trap behavior, i.e., the instruction that changed the TE field in the PSW may or may not cause a trace trap. Accordingly, only microsequence instructions should be used to change the TE field state.

Bits 18 through 21 – Condition Codes (NZVC). Bits 18 through 21 represent condition codes. These codes reflect the status of the last instruction execution to affect them. The codes are tested by using the conditional branch instructions and indicate the following when set:

| Ν | _ | Negative | (bit 21) |

|---|---|----------|----------|

| Ζ | _ | Zero     | (bit 20) |

| ۷ | _ | Overflow | (bit 19) |

| С |   | Carry    | (bit 18) |

**Bit 22** – Enable Overflow Trap (DE). Bit 22, when set, enables overflow traps. It is cleared whenever an overflow trap is detected and handled.

**Bit 23 – Cache Disable (CD).** Bit 23 enables and disables the instruction cache. When the CD bit is cleared, the cache is used to store and read text. When the CD bit is set, the cache is not used. The instruction cache should be disabled only when its use could cause problems, e.g., when self-modifying code is executing. Changes to the CD field via instructions that have the PSW as an explicit destination may corrupt the contents of the instruction cache. Therefore, only microsequence instructions should be used to change the CD field state.

**Bit 24 – Quick-Interrupt Enable (QIE).** Bit 24 enables and disables the quick-interrupt facility. If QIE is set, an interrupt is handled via the quick- interrupt sequence. If QIE is cleared, the interrupt causes a process switch (full-interrupt sequence).

**Bit 25 – Cache Flush Disable (CFD).** Bit 25, when set, disables instruction cache flushing (emptying of the cache's contents) when a new process is loaded via the XSWITCH\_TWO microsequence (see Microsequences). When cleared, the contents of the cache are flushed when a new process is loaded via the XSWITCH\_TWO microsequence.

Bits 26 through 31 – Unused. Bits 26 through 31 are not used and must always be cleared.

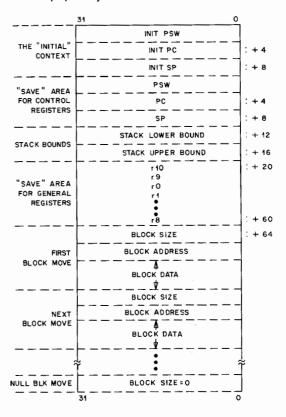

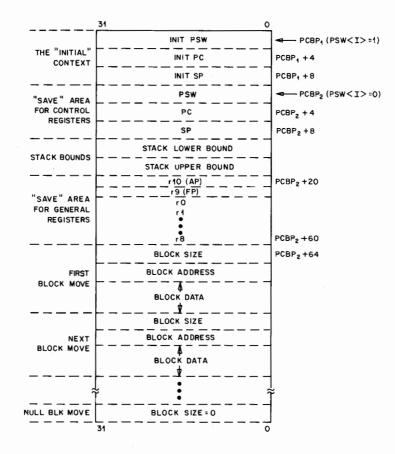

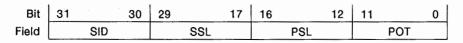

#### Process Control Block (PCB)

The PCB contains the entire switchable process context, collected into a compact form for ease of movement between system memory and privileged internal registers. The process control block pointer (PCBP), r13, contains the address of the PCB currently in execution. The PCB is shown on Figure 4 and a summary of its contents appears in Table 2.

#### Interrupts

The microprocessor accepts fifteen levels of interrupt requests from a 4-bit interrupt request input port (IPL0--IPL3); it also accepts a nonmaskable interrupt if **NMINT** is externally asserted. The pending interrupt value input on IPL0-IPL3 is internally inverted and compared to the value contained in the interrupt priority level (IPL) field of the PSW. In order for the pending interrupt to be acknowledged, its inverted value must be greater than the IPL field value. Pending interrupts whose inverted values are less than or equal to the IPL field value are ignored. The exception to this is a nonmaskable interrupt, which can interrupt the microprocessor regardless of the present interrupt priority level.

Figure 4. Process Control Block

The microprocessor acknowledges an interrupt by transmitting the inverted interrupt value on bits 2 through 5 of the address bus. In addition, the value placed on the interrupt option (INTOPT) pin is inverted and transmitted on bit 6 of the address bus. The microprocessor then fetches the interrupt vector number from the interrupting device on bits 0 through 7 of the data bus and begins execution of the interrupt handling routine.

Table 3 shows the interrupt priority levels and the corresponding interrupt acknowledges output by the microprocessor.

Autovector, nonmaskable-interrupt, and quickinterrupt facilities are also available. The microprocessor provides the vector number for

the interrupting device if the autovector input (AVEC) is asserted at the same time as the interrupt request. The vector number is dependent on the interrupt's priority level. If the nonmaskable interrupt (NMINT) input is asserted, the interrupt occurs but is treated as an autovector interrupt with the vector number 0. During the acknowledge cycle of a nonmaskable interrupt, the microprocessor address bus contains all zeros. This distinguishes a nonmaskable interrupt from all other interrupts. A nonmaskable interrupt can interrupt the microprocessor regardless of the current priority. Interrupts are handled via the quick-interrupt sequence if the quick-interrupt enable (QIE) bit in the PSW is set. Table 4 summarizes how the microprocessor handles the various interrupt requests.

| Table 2. | Process | Control | BIOCK | Section |  |

|----------|---------|---------|-------|---------|--|

|          |         |         |       |         |  |

| PCB Section                     | Description                                                                                                                                                                                                             |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Initial context                 | This section contains a set of initial values for the PSW, PC, and SP. This allows a process to be restarted with its initial values even though, at some point, its execution is suspended.                            |

| Save area for control registers | This section contains the PSW, PC, and SP values at the time the current process is switched.                                                                                                                           |

| Stack bounds                    | This section defines the upper and lower bounds of the stack<br>used in the current process. It contains pointers to the upper<br>and lower memory limits of the stack.                                                 |

| Save area for general registers | This section contains images of what registers 0 through 10 (r0—r10) were when the process was switched. This allows the process to continue in the same state that it was in when control switched to another process. |

| First block move                | Moves data in PCB to an arbitrary memory region.                                                                                                                                                                        |

| Next & nth block move           | Moves a different set of data in PCB to a different memory region.                                                                                                                                                      |

| Null block move                 | Terminates block move sequence.                                                                                                                                                                                         |

|        | Inter<br>Req<br>Inp<br>PL0-<br>Bi | uest<br>out<br>-IPL |        | Interrupt<br>Option<br>Input<br>INTOPT | Interrupt<br>Acknowledge<br>Output<br>ADDR02—ADDR06<br>Bits |        |        |        | Priority<br>Level in<br>Descending<br>Order |                      |

|--------|-----------------------------------|---------------------|--------|----------------------------------------|-------------------------------------------------------------|--------|--------|--------|---------------------------------------------|----------------------|

| 3      | 2                                 | 1                   | 0      |                                        | 06                                                          | 05     | 04     | 03     | 02                                          |                      |

| 0<br>0 | 0<br>0                            | 0<br>0              | 0<br>0 | 0<br>1                                 | 1<br>0                                                      | 1      | 1<br>1 | 1      | 1<br>1                                      | Highest<br>priority  |

| 0<br>0 | 0<br>0                            | 0<br>0              | 1<br>1 | 0<br>1                                 | 1<br>0                                                      | 1      | 1<br>1 | 1      | 0<br>0                                      | 2nd                  |

| 0      | 0                                 | 1                   | 0<br>0 | 0                                      | 1<br>0                                                      | 1      | 1      | 0<br>0 | 1                                           | 3rd                  |

| 0      | 0<br>0                            | 1                   | 1      | 0                                      | 1<br>0                                                      | 1      | 1      | 0<br>0 | 0<br>0                                      | 4th                  |

| 0      | 1                                 | 0<br>0              | 0<br>0 | 0<br>1                                 | 1                                                           | 1.     | 0<br>0 | 1      | 1                                           | 5th                  |

| 0      | 1                                 | 0<br>0              | 1      | 0<br>1                                 | 1<br>0                                                      | 1      | 0<br>0 | 1      | 0<br>0                                      | 6th                  |

| 0      | 1                                 | 1                   | 0<br>0 | 0                                      | 1<br>0                                                      | 1      | 0<br>0 | 0<br>0 | 1                                           | 7th                  |

| 0      | 1                                 | 1                   | 1      | 0                                      | 1                                                           | 1      | 0      | 0      | 0                                           | 8th                  |

| 1      | 0                                 | 0                   | 0      | 0                                      | 1<br>0                                                      | 0      | 1      | 1      | 1                                           | 9th                  |

| 1      | 0<br>0                            | 0                   | 1      | 0                                      | 1                                                           | 0      | 1      | 1      | 0<br>0                                      | 10th                 |

| 1      | 0                                 | 1                   | 0      | 0                                      | 1                                                           | 0<br>0 | 1      | 0      | 1                                           | 11th                 |

| 1      | 0                                 | 1                   | 1<br>1 | 0                                      | 1                                                           | 0      | 1      | 0      | 0<br>0                                      | 12th                 |

| 1      | 1                                 | 0                   | 0      | 0                                      | 1                                                           | 0      | 0      | 1      | 1                                           | 13th                 |

| 1      | 1                                 | 0                   | 1      | 0                                      | 1                                                           | 0      | 0      | 1      | 0                                           | 14th                 |

| 1      | 1                                 | 1                   | 0      | 0                                      | 1                                                           | 0      | 0      | 0      | 1                                           | Lowest<br>priority   |

| 1      | 1                                 | 1<br>1              | 1      | 0                                      | x<br>x                                                      | x<br>x | x<br>x | x<br>x | x<br>x                                      | No interrupt pending |

Table 3. Interrupt Level Code Assignments

Note: x = no value placed on address bus.

| Priority<br>of Interrupt                              | Interrupt<br>Acknowledge | AVEC | NMINT | QIE | Result                                                                                                                                                                                                   |

|-------------------------------------------------------|--------------------------|------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Less than<br>PSW IPL field<br>priority                | No                       | x    | 1     | x   | Interrupt is not acknowledged.                                                                                                                                                                           |

| Equal to<br>PSW IPL field<br>priority                 | No                       | x    | 1     | x   | Interrupt is not acknowledged.                                                                                                                                                                           |

| Greater than<br>PSW IPL field<br>priority             | Yes                      | 1    | 1     | 0   | Interrupt is acknowledged via full-interrupt sequence. Microprocessor fetches vector number from interrupting device.                                                                                    |

| Greater than<br>PSW IPL field<br>priority             | Yes                      | 0    | 1     | 0   | Interrupt is acknowledged via full-interrupt sequence. Microprocessor supplies the vector number.                                                                                                        |

| Any level<br>compared to<br>PSW IPL field<br>priority | Yes                      | x    | 0     | 0   | Interrupt is acknowledged via full-interrupt<br>sequence. It is treated as an autovector at<br>vector number 0. The address bus<br>contains all zeros during the acknowledge.                            |

| Greater than<br>PSW IPL field<br>priority             | Yes                      | 1    | 1     | 1   | Interrupt is acknowledged and serviced via<br>quick-interrupt sequence. Microprocessor<br>fetches vector number from interrupting<br>device.                                                             |

| Greater than<br>PSW IPL field<br>priority             | Yes                      | 0    | 1     | 1   | Interrupt is acknowledged and serviced via<br>quick-interrupt sequence. Microprocessor<br>supplies the vector number.                                                                                    |

| Any level<br>compared to<br>PSW IPL field<br>priority | Yes                      | x    | 0     | 1   | Interrupt is acknowledged and serviced via<br>quick-interrupt sequence. It is treated as<br>an autovector interrupt at vector number 0.<br>The address bus contains all zeros during<br>the acknowledge. |

### Table 4. Interrupt Acknowledge Summary

Note: x = don't care.

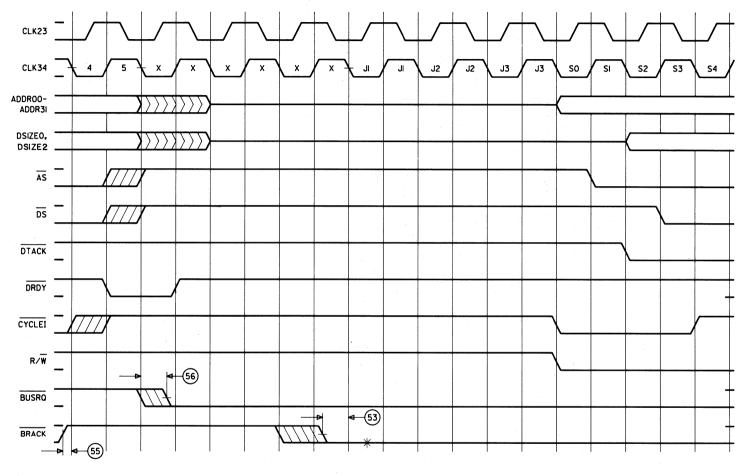

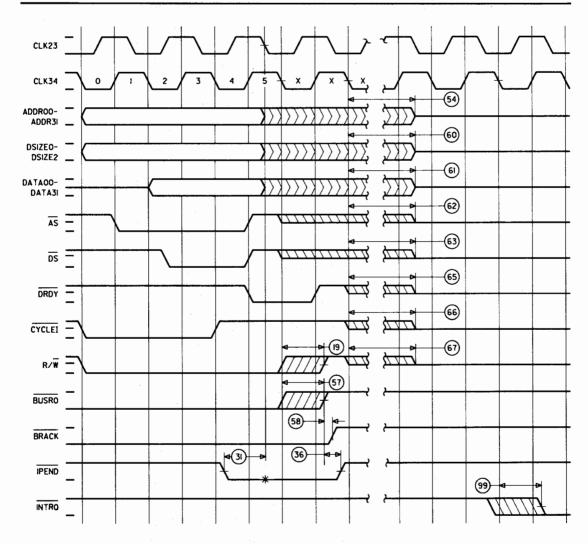

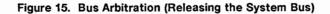

#### **Bus Arbitration**

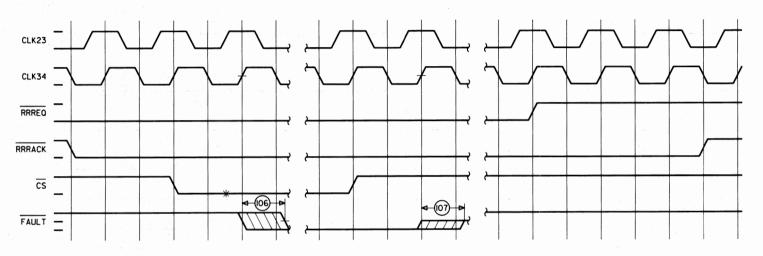

The microprocessor arbitrates requests for its bus (relinquish and retry request, RRREQ, an bus request, BUSRQ) in the following manner. An RRREQ is acknowledged only during a bus transaction; however, it is ignored during the write portion of a read-interlocked transaction. An RRREQ has priority over a BUSRQ. A BUSRQ is not acknowledged until the end of a bus transaction or until the end of the write portion of a read-interlocked transaction. A bus request is acknowledged immediately if the bus is idle.

#### Direct Memory Access and Multiprocessor Support

The microprocessor provides support for direct memory access (DMA) and shares bus control responsibilities with the system DMA controller. To initiate a DMA operation, the controller must request the microprocessor bus by asserting the BUSRQ input. Once the microprocessor recognizes the request, it drives its outputs to the states given in Table 5. The microprocessor then acknowledges the DMA request by asserting the bus request acknowledge (BRACK) output. Upon completion of the DMA operation, the 3-stated signals are returned to the microprocessor's control.

The microprocessor provides for the support of multiprocessors via the  $\overline{\text{BARB}}$  pin. When this signal is asserted, the microprocessor assumes the role of bus arbiter and other devices request the bus from the microprocessor. When the signal is not asserted, the microprocessor must request the bus from an external bus arbiter. The ability to reassign the bus arbiter provides the capability to have a multiprocessor system.

#### **Coprocessor Interface**

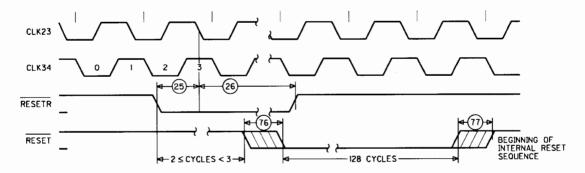

The coprocessor interface consists of ten instructions and the associated pinout and protocol. This interface is provided to insure high performance of coprocessors, thus increasing overall system throughput.

#### **Read-Interlocked Operation**

The microprocessor provides an interlocked operation that prevents another processor from accessing a memory location between the read and write halves of the operation. Interlocked

#### Table 5. Output States After DMA Request Acknowledge

| Output Signal  | Signal State |

|----------------|--------------|

| ABORT          | Z'           |

| ADDR00-ADDR31  | Z            |

| ĀS             | Z'           |

| BRACK          | Logic 0      |

| CYCLEI         | Z'           |

| DATA00-DATA31  | Z            |

| DRDY           | Z'           |

| DS             | Z'           |

| DSIZE0, DSIZE1 | Z            |

| R/W            | Z'           |

| RESET          | Logic 1      |

| RRRACK         | Logic 1      |

| SAS0—SAS3      | Ζ'           |

| VAD            | Z            |

| XMD0, XMD1     | Z            |

Notes:

Z = High-impedance.

Z' - High-impedance. Normally tied high with external passive holding resistor.

operation consists of a memory fetch (read access) and one or more internal microprocessor operations, followed by a write access to the same memory location. Once the read access has been completed, the interlocked operation may not be preempted other than by a reset.

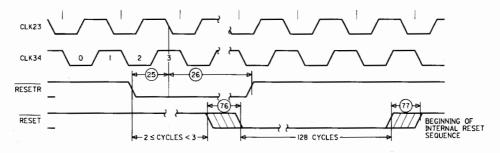

#### Reset

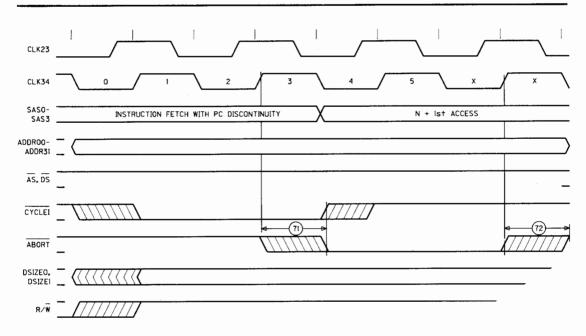

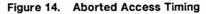

Two types of reset requests are available system-initiated and microprocessor-initiated. Both requests have highest priority and preempt any ongoing microprocessor operation. A system-initiated reset differs from a microprocessor-initiated reset only because it is externally generated. The system initiates a reset by driving the reset request (RESETR) input low. Once the microprocessor recognizes the request, it sends a reset acknowledge (RESET) to the system and drives its outputs to a temporary state, which prevents control signal and bus conflicts while the system is responding to the acknowledge. The system negates RESETR once it has responded to the acknowledge, but the microprocessor continues to hold RESET active for an additional 128 clock cycles, allowing the external system to go through its own initialization sequence. At the end of this period, the microprocessor negates RESET and begins execution of the internal reset sequence. Table 6 indicates the states of the microprocessor's output pins once it has negated RESET. The microprocessor must perform the following register initialization sequence before operations begin again (restart):

- Initiate physical addressing mode.

- Fetch a word at location 80 (hexadecimal) and put it into the process control block pointer (r13). This word is the beginning address of the reset process control block (PCB).

- Fetch a word at the PCB address and store it in the PSW.

- Fetch a word at the location four bytes from the initial PCB address and store it in the program counter (PC). This word is the PC value for initial execution.

- Fetch word at the location eight bytes from the initial PCB address and store it in the stack pointer (SP).

The microprocessor then begins execution at the address specified by the PC.

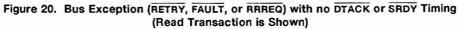

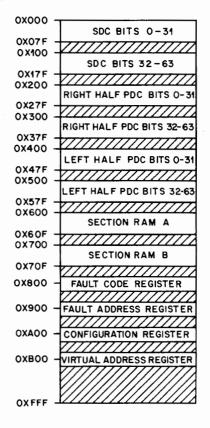

# Flags/Conditions