# IeeeCC754++ An Advanced Set of Tools to Check IEEE 754-2008 Conformity

# MATTHIAS HÜSKEN

## DISSERTATION

zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

Vorgelegt und genehmigt an der Fakultät für Mathematik und Naturwissenschaften der Bergischen Universität Wuppertal

Gutachter: Prof. Dr. Andreas FROMMER Prof. Dr. Dirk Pleiter Prüfungskommission: Prof. Dr. Andreas FROMMER Prof. Dr. Dirk PLEITER Prof. Dr. Bruno LANG Prof. Dr. Michael GÜNTHER

Wuppertal, 06.12.2017

Die Dissertation kann wie folgt zitiert werden:

urn:nbn:de:hbz:468-20180213-104430-5 [http://nbn-resolving.de/urn/resolver.pl?urn=urn%3Anbn%3Ade%3Ahbz%3A468-20180213-104430-5]

# Danksagungen

Am Anfang dieser Arbeit möchte ich die Gelegenheit nutzen, mich bei denen zu bedanken, die mich über die Jahre begleitet haben und ohne die es nicht zur Entstehung dieses Werkes gekommen wäre. Mein Dank gilt zuerst Prof. Dr. Andreas Frommer für die Möglichkeit, diese Arbeit zu verfassen, für seine Betreuung und die wertvollen Hinweise sowie die angenehme Atmosphäre in seiner Arbeitsgruppe. Darüber hinaus ermöglichte er mir die Mitarbeit an verschiedensten interessanten Projekten, allen voran QPACE und QPACE3. Ebenso danke ich Prof. Dr. Dirk Pleiter für die wertvollen Anregungen zu dieser Arbeit, die langjährige gute Zusammenarbeit im QPACE-Projekt und das unkomplizierte Zurverfügungstellen einer Reihe von Testplattformen. Prof. Dr. Bruno Lang danke ich vor allem für die zahlreichen inspirierende Unterhaltungen jedweder Art.

Dank netter (ehemaliger und aktueller) Kollegen durfte ich in der Arbeitsgruppe Angewandte Informatik in angenehmer Umgebung arbeiten. Namentlich nennen möchte ich hier Brigitte Schultz, ohne die diese Arbeitsgruppe schon längst zusammengebrochen wäre, Katrin, Holger, Peter, Sonja, Marcel, Jan, Claudia, Artur und Martin. Vielen Dank auch an Willi für die Bereitstellung weiterer Testplattformen sowie an Sonja, Martin, Sarah, Jared und meinen Vater für das Korrekturlesen und die Hilfe bei diversen LAT<sub>F</sub>X- und Englisch-Fragen.

Weiterer Dank gilt meinen Freunden, mit denen ich die Abenteuer Musik (new challenge) und Kirche (NORDSTERN.kirche) erleben durfte und darf: Alex und Heike, Andre und Anne, Simon und Bine, Gary und Nic, Gerrith und Miri (und meinen wunderbaren Patenkindern Noah, Leah und Ewah), Sontka, Stephan und Verena, Kris und vielen weiteren.

Vielen Dank meiner Familie: meinen Geschwistern und deren Ehepartnern und Kindern, und vor allem meinen Eltern, ohne deren vielfältige Unterstützung es diese Arbeit nicht gegeben hätte.

Jen – du bist das Beste, was mir passieren konnte. Danke für alles!

Und das Wichtigste zum Schluss – meinem Gott: "Denn von ihm und durch ihn und für ihn sind alle Dinge." (Die Bibel, Römerbrief, Kapitel 11, Vers 36) Soli deo gloria.

# Contents

1

# Introduction

| 1 | Floa | nting-po | oint numbers, standards, and the user environment 5                                               |

|---|------|----------|---------------------------------------------------------------------------------------------------|

|   | 1.1  |          | undation: Floating-point numbers 6                                                                |

|   | 1.2  | The st   | andards: IEEE 754 and 854                                                                         |

|   |      | 1.2.1    | IEEE 754                                                                                          |

|   |      | 1.2.2    | IEEE 854 14                                                                                       |

|   |      | 1.2.3    | IEEE 754-2008                                                                                     |

|   |      | 1.2.4    | IEEE 754-2018                                                                                     |

|   | 1.3  | Round    | ing and error analysis                                                                            |

|   |      | 1.3.1    | Some basic properties                                                                             |

|   |      | 1.3.2    | Stability                                                                                         |

|   |      | 1.3.3    | Use cases for rounding $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 22$ |

|   | 1.4  | The us   | ser environment                                                                                   |

|   |      | 1.4.1    | Limitations of the user environment definition                                                    |

|   |      | 1.4.2    | Floating-point hardware                                                                           |

|   |      | 1.4.3    | The operating system                                                                              |

|   |      | 1.4.4    | Floating-point libraries                                                                          |

|   |      | 1.4.5    | Programming languages                                                                             |

|   |      | 1.4.6    | The compiler's role                                                                               |

|   |      | 1.4.7    | Interpreters                                                                                      |

|   |      | 1.4.8    | In-network floating-point computations                                                            |

|   |      | 1.4.9    | Resilience                                                                                        |

|   |      | 1.4.10   | Comparing and testing floating-point environments 38                                              |

| 2 | Ieee | eCC754   | 39                                                                                                |

|   | 2.1  | Histor   | y                                                                                                 |

|   | 2.2  | IeeeC    | 2754                                                                                              |

|   | 2.3  | Testset | ts $\ldots \ldots 43$  |

|---|------|---------|--------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.3.1   | Addition and subtraction                                                                                                 |

|   |      | 2.3.2   | Multiplication                                                                                                           |

|   |      | 2.3.3   | Division                                                                                                                 |

|   |      | 2.3.4   | Square root                                                                                                              |

|   |      | 2.3.5   | Remainder                                                                                                                |

|   |      | 2.3.6   | A note on conversions                                                                                                    |

|   |      | 2.3.7   | Conversions between floating-point formats                                                                               |

|   |      | 2.3.8   | Rounding floating-point numbers to integral values 46                                                                    |

|   |      | 2.3.9   | Conversion between floating-point and integer formats 46                                                                 |

|   |      | 2.3.10  | Decimal to binary and binary to decimal conversion 46                                                                    |

|   | 2.4  | Result  | s                                                                                                                        |

|   |      | 2.4.1   | Intel and AMD 47                                                                                                         |

|   |      | 2.4.2   | SUN Sparc                                                                                                                |

|   |      | 2.4.3   | FMLib                                                                                                                    |

|   |      | 2.4.4   | MpIeee                                                                                                                   |

| 3 | Ieee | CC754+  | + 51                                                                                                                     |

|   | 3.1  | IeeeCO  | C754++: Introducing extensions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 52$                              |

|   |      | 3.1.1   | Testing IEEE-conformity                                                                                                  |

|   |      | 3.1.2   | Testing the user environment: Default mode                                                                               |

|   |      | 3.1.3   | Testing parts of a floating-point environment                                                                            |

|   |      | 3.1.4   | Testing distributed floating-point environments 57                                                                       |

|   |      | 3.1.5   | Supporting arbitrary floating-point environments 58                                                                      |

|   |      | 3.1.6   | Building for arbitrary environments 61                                                                                   |

|   |      | 3.1.7   | Large-scale testing and analysis                                                                                         |

|   |      | 3.1.8   | Studying the influence of compiler options                                                                               |

|   |      | 3.1.9   | Testing modes                                                                                                            |

|   |      | 3.1.10  | Input and output                                                                                                         |

|   |      | 3.1.11  | Support for IEEE 754-2008                                                                                                |

|   |      | 3.1.12  | Analysis capabilities                                                                                                    |

|   |      | 3.1.13  | Preserving backwards compatibility                                                                                       |

|   |      | 3.1.14  | Technical changes                                                                                                        |

|   | 3.2  | Input   | and output $\ldots \ldots 77$ |

|   |      | 3.2.1   | Test vector formats                                                                                                      |

|   |      | 3.2.2   | Output formats                                                                                                           |

|   | 3.3  | Testing | g modes $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 80                                       |

|   |      | 3.3.1   | Classic mode                                                                                                             |

|   |      | 3.3.2   | Verbose mode                                                                                                             |

|   |      | 3.3.3   | Default mode                                                                                                             |

|   |      | 3.3.4   | Distributed computing modes                                                                                              |

|   |      | 3.3.5   | Miscellaneous modes                                                                                                      |

|   |      | 3.3.6   | Common command line options                                                                                              |

\_\_\_\_\_

|   | 3.4 | The evaluation framework                                                                                                                       |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.4.1 Using the evaluation framework                                                                                                           |

|   |     | $3.4.2$ Analysis modules $\ldots \ldots 112$ |

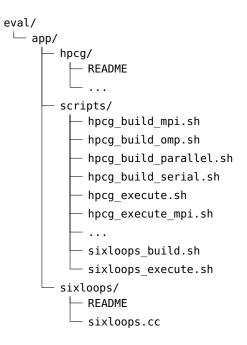

|   |     | 3.4.3 Tools for (semi-)automated testing                                                                                                       |

|   | 3.5 | The optimisation framework                                                                                                                     |

|   |     | 3.5.1 Using the optimisation framework                                                                                                         |

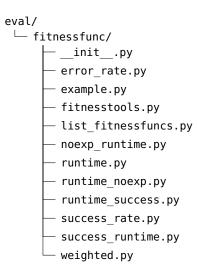

|   |     | 3.5.2 Fitness modules and adding fitness functions                                                                                             |

|   |     | 3.5.3 Timing the effect of compiler options                                                                                                    |

| 4 | Ext | ended testsets 147                                                                                                                             |

| - | 4.1 | General considerations                                                                                                                         |

|   | 1.1 | 4.1.1 The Table Maker's Dilemma                                                                                                                |

|   |     | 4.1.2 Adding operators and test vectors                                                                                                        |

|   | 4.2 | Fused multiply-add                                                                                                                             |

|   | 1.2 | 4.2.1 Testset                                                                                                                                  |

|   |     | 4.2.2 Considerations concerning portability                                                                                                    |

|   | 4.3 | Powers and roots                                                                                                                               |

|   | 1.0 | $4.3.1$ Testsets $\ldots$ $154$                                                                                                                |

|   | 4.4 | Trigonometric functions                                                                                                                        |

|   |     | 4.4.1 Testsets                                                                                                                                 |

|   | 4.5 | Exponentials and logarithms                                                                                                                    |

|   |     | 4.5.1 Testsets                                                                                                                                 |

|   | 4.6 | Miscellaneous functions                                                                                                                        |

|   |     | 4.6.1 Testsets                                                                                                                                 |

|   | 4.7 | Generating testsets                                                                                                                            |

|   |     | 4.7.1 A note on precisions $\ldots \ldots 158$             |

|   |     | 4.7.2 convertTestsets.py                                                                                                                       |

|   |     | 4.7.3 genUCB.sh                                                                                                                                |

| 5 | Arc | hitecture ports 165                                                                                                                            |

| • | 5.1 | The default architecture                                                                                                                       |

|   | 0   | 5.1.1 The default port                                                                                                                         |

|   |     | 5.1.2 The dummy port                                                                                                                           |

|   | 5.2 | The x86 architecture $\ldots \ldots 175$                   |

|   | -   | 5.2.1 The <b>x86</b> port                                                                                                                      |

|   |     | 5.2.2 The mic port                                                                                                                             |

|   | 5.3 | The ARM architecture                                                                                                                           |

|   |     | 5.3.1 The arm port                                                                                                                             |

|   |     | 5.3.2 The aarch64 port                                                                                                                         |

|   | 5.4 | The Power Architecture                                                                                                                         |

|   |     | 5.4.1 The ppc port $\ldots$ $184$                                                                                                              |

|   |     | 5.4.2 The cell port                                                                                                                            |

|   |     | 5.4.3 The <b>bgq</b> port                                                                                                                      |

|   | 5.5        | GPUs and accelerators                                                                                                                             |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | 5.5.1 The <b>nv</b> port                                                                                                                          |

|   |            | 5.5.2 The opencl port                                                                                                                             |

|   | 5.6        | In-network computations                                                                                                                           |

|   |            | 5.6.1 The <b>mpi</b> port                                                                                                                         |

|   | 5.7        | Virtual machines and software libraries                                                                                                           |

|   |            | 5.7.1 The java port                                                                                                                               |

|   |            | 5.7.2 The softfloat port                                                                                                                          |

|   |            | 5.7.3 The mpfr port                                                                                                                               |

|   |            | 5.7.4 The crlibm port                                                                                                                             |

| 6 | Sele       | ted results 201                                                                                                                                   |

| U | 6.1        | A detailed example                                                                                                                                |

|   | 0.1        | $6.1.1$ User environments $\ldots \ldots 202$          |

|   |            | 6.1.2 Manual testing procedure                                                                                                                    |

|   |            | 6.1.3 (Semi-)Automated testing procedure                                                                                                          |

|   |            | $6.1.4$ Analysing the logfiles $\ldots \ldots 217$                   |

|   | 6.2        | Different compilers                                                                                                                               |

|   | 6.3        | 1                                                                                                                                                 |

|   | 0.5        | x86                                                                                                                                               |

|   |            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                              |

|   | 6.4        |                                                                                                                                                   |

|   | 0.4        | -                                                                                                                                                 |

|   |            |                                                                                                                                                   |

|   | 6.5        |                                                                                                                                                   |

|   | 0.0        |                                                                                                                                                   |

|   |            | $6.5.1  \text{POWER8}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                           |

|   | <i>c c</i> | $6.5.2  \text{Cell}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                             |

|   | 6.6        | Accelerators $\ldots \ldots 253$  |

|   |            | $6.6.1  \text{CUDA}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                             |

|   | 0 7        | $6.6.2  \text{OpenCL}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                           |

|   | 6.7        | Software                                                                                                                                          |

|   |            | $6.7.1  \text{SoftFloat}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                        |

|   |            | $6.7.2 \text{ MPFR} \dots 259$                                                                                                                    |

|   |            | 6.7.3 Java                                                                                                                                        |

|   | 6.8        | Elementary functions                                                                                                                              |

|   |            | 6.8.1 C99 vs. C++11                                                                                                                               |

|   |            | 6.8.2 Trigonometric operators                                                                                                                     |

|   |            | 6.8.3 Exponentials and logarithms                                                                                                                 |

|   |            | $6.8.4  \text{Power operators} \dots \dots$ |

|   |            | 6.8.5 roundTiesToEven results                                                                                                                     |

|   | 6.9        | Optimisation framework                                                                                                                            |

|   |            | 6.9.1 User environments                                                                                                                           |

|   |            | 6.9.2 Two-step process $\ldots \ldots 274$                                         |

|    |      | 6.9.3   | Example run with sixloops                   |       |   |       |   |   | 277 |

|----|------|---------|---------------------------------------------|-------|---|-------|---|---|-----|

|    |      | 6.9.4   | Example run with HPCG                       |       |   |       |   |   | 279 |

|    | 6.10 | Result  | summary                                     |       |   |       |   |   | 280 |

|    |      | 6.10.1  | Basic operations and conversions            |       |   |       |   |   | 281 |

|    |      | 6.10.2  | Elementary operators                        |       |   |       |   |   | 282 |

|    |      | 6.10.3  | Some notes on applications                  |       | • |       |   |   | 283 |

| Su | mma  | ry and  | outlook                                     |       |   |       |   |   | 285 |

| Α  | The  | IeeeCC  | 754++ build system                          |       |   |       |   |   | 289 |

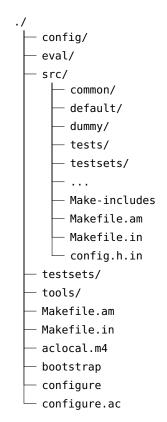

|    | A.1  | Chang   | es to the code base                         |       |   |       |   |   | 289 |

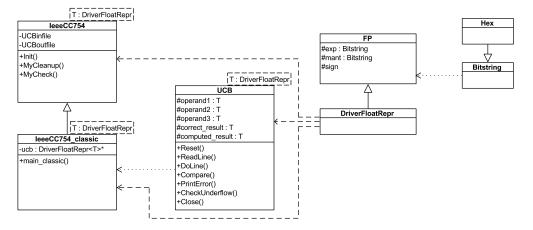

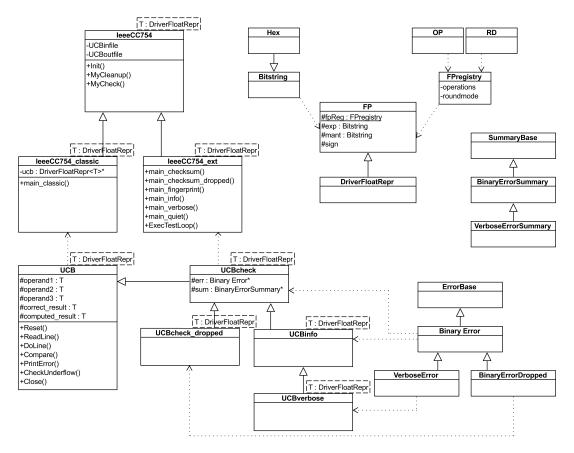

|    |      | A.1.1   | IeeeCC754 code structure                    |       |   |       |   |   | 290 |

|    |      | A.1.2   | IeeeCC754++ code structure                  |       |   |       |   |   | 291 |

|    | A.2  | The bu  | uild system                                 |       |   |       |   |   | 292 |

|    | A.3  | Config  | uring and building IeeeCC754++              |       |   |       |   |   | 295 |

|    |      | A.3.1   | Building overview                           |       |   |       |   |   | 295 |

|    |      | A.3.2   | Choosing an architecture                    |       |   |       |   |   | 296 |

|    |      | A.3.3   | Choosing FPUs                               |       |   |       |   |   | 296 |

|    |      | A.3.4   | Choosing the compiler and compiler options  |       |   |       |   |   | 297 |

|    |      | A.3.5   | Generic build features                      |       |   |       |   |   | 298 |

|    |      | A.3.6   | Additional build options                    |       |   |       |   |   | 300 |

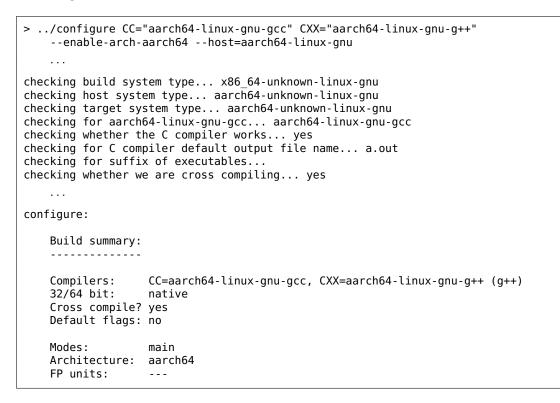

|    |      | A.3.7   | Cross compilation                           |       |   |       |   |   | 301 |

|    |      | A.3.8   | Building historic modes                     |       |   |       |   |   | 303 |

|    |      | A.3.9   | A detailed example                          | <br>• | • | <br>• | • | • | 304 |

| В  | Addi | ing a n | ew architecture to IeeeCC754++              |       |   |       |   |   | 307 |

|    | B.1  | File st | ructure                                     |       |   |       |   |   | 307 |

|    | B.2  | Build a | system: configure.ac                        |       |   |       |   |   | 308 |

|    | B.3  | Build a | system: Makefile.am                         |       |   |       |   |   | 311 |

|    | B.4  | Impler  | nenting the new architecture                |       |   |       |   |   | 311 |

|    |      | B.4.1   | <pre>src/xyz/DriverFloat_main.h</pre>       |       |   |       |   |   | 312 |

|    |      | B.4.2   | <pre>src/xyz/fpu_main.cc</pre>              |       |   |       |   |   | 315 |

|    | B.5  | Adding  | g an FPU                                    |       |   |       |   |   | 316 |

|    | B.6  | Impler  | nenting an operation                        |       |   |       |   |   | 317 |

|    | B.7  | Handli  | ng vector FPUs                              |       |   |       |   |   | 321 |

|    | B.8  |         | sing an FPU                                 |       |   |       |   |   | 323 |

|    |      | B.8.1   | Registering operations and rounding modes   |       |   |       |   |   | 323 |

|    |      | B.8.2   | Enabling vector FPUs                        |       |   |       |   |   | 327 |

|    | B.9  | Examp   | ble code for the new architecture and FPU . |       |   |       |   |   | 328 |

|    | B.10 |         | g up main()                                 |       |   |       |   |   | 330 |

|    |      |         | g up and building the new architecture      |       |   |       |   |   | 331 |

v

| С   | Refe   | rence material                  | 333 |

|-----|--------|---------------------------------|-----|

|     | C.1    | fma example                     | 333 |

|     | C.2    | IeeeCC754++ usage               | 334 |

|     | C.3    | IeeeCC754++ classic mode usage  | 335 |

|     | C.4    | Error codes used in IeeeCC754++ | 336 |

|     | C.5    | Reference task files            | 338 |

|     | C.6    | Evaluation function example     | 346 |

|     | C.7    | Fitness function example        | 348 |

| Lis | t of   | Figures                         | 351 |

| Lis | t of   | Tables                          | 354 |

| Lis | t of   | Listings                        | 355 |

| Bil | oliogr | raphy                           | 361 |

# Introduction

The "IEEE Standard for Binary Floating-Point Arithmetic" IEEE 754 has arguably been one of the most influential standards for the broad area of scientific computing. Since its publication in 1985, it is the benchmark for the quality of floating-point implementations of processors and floating-point units. Floating point arithmetic conforming to the standard implies that numerical algorithms behave identically across the various computing platforms (or at least in a predictable manner) and that developers of numerical algorithms can rely on the standard when addressing stability issues that might otherwise depend on the floating-point environment. The standard thus facilitates the portability of numerical algorithms across platforms.

With this thesis, we provide a contribution to evaluating the conformity of a given floating-point environment to the latest valid version of the standard. In particular, we extended the well known testing tool **IeeeCC754** with a large number of features, such as support for the current incarnation of the standard called IEEE 754-2008, new analysis facilities, additional floating-point operators, and new test vectors to verify that these operators are implemented in a conforming manner. Furthermore, we heavily expanded the selection of supported floatingpoint environments and provide facilities to easily extend our new tool IeeeCC754++ with new ports targeted at future floating-point platforms. We meticulously documented the process of adding a new architecture port and demonstrate its applicability with a port for the ARM SVE floating-point unit (for which hardware is not yet available). Additionally, we developed a testing framework that enables large-scale evaluation of floating-point environments, the graphical application **IeeeCC754++LogViewer** that provides convenient access to the generated logfiles, and a variation of the testing framework tailored to studying the influence of compiler options on the behaviour of numerical applications regarding floatingpoint accuracy as well as application performance.

Former testing tools including **IeeeCC754** serve a rather technical purpose, i. e. they enable developers and implementers of floating-point units (be it hardware units or software libraries) to verify proper functionality of their implementation. This use case is also supported by **IeeeCC754++**; however, our tool takes a more user centric point of view by enabling the average researcher with the possibility to check her default floating-point environment (which is called default user environment in this thesis) for IEEE 754-2008 conformity.

The thesis is organised as follows: In Chapter 1, we give a short introduction of floating-point numbers and their properties and take a look at the different incarnations of IEEE 754-2008. Afterwards, we define the term user environment and discuss the components that constitute such an environment. Chapter 2 presents former work in providing tools for testing the IEEE-conformity of a floating-point implementation. In particular, we describe **IeeeCC754** which represents the tool that **IeeeCC754++** is based upon, discuss its testing model, and briefly summarise results from former conformity testing.

Chapters 3 to 5 constitute the main part of this thesis in which we describe our contributions to IEEE-conformity testing. Chapter 3 starts with a more detailed discussion of testing strategies and our definition of a user environment, followed by an in-depth look at the new features which we implemented in IeeeCC754++. Additionally, we discuss different testing modes targeted at a range of applications such as default user environment testing or IEEE-conformity evaluation of specific floating-point units. We introduce the evaluation and optimisation frameworks which support large-scale testing and studying the influence of compiler options, and present a few additional tools that ease the analysis of the resulting logfiles such as the graphical application **IeeeCC754++LogViewer**. Chapter 4 starts with a description of the floating-point operators which were not part of the original IEEE 754 standard, but which were introduced with IEEE 754-2008, e.g. a fused multiply-add operator and a range of elementary operators such as trigonometric functions or exponentials. We then describe the test vectors which we added to the original **IeeeCC754** testsets in order to check the new floating-point operators. The discussion of the numerous architecture ports which we implemented in IeeeCC754++ is the subject of Chapter 5. We describe the various underlying classes of platforms such as hardware floating-point units of different processors, accelerators, or software libraries, give a short overview of the history and the corresponding instruction sets or implementations of the respective platforms, and finally discuss their integration into our testing tool IeeeCC754++.

In order to demonstrate the use of our contributions regarding IEEE-conformity testing, Chapter 6 presents results for a selection of the architecture ports described in Chapter 5. We also show how to apply the extended tools such as the evaluation and optimisation frameworks or IeeeCC754++LogViewer during the testing process. We conclude this thesis by summarising the contributions presented in this thesis and discussing further possible research areas.

Since the extension with further architecture ports is an integral part of our contributions to IEEE-conformity testing, we add three corresponding appendices to this thesis. Appendix A discusses the structure of the IeeeCC754++ source code together with the newly written build system and describes the process of building and running IeeeCC754++ executables. In Appendix B, we give detailed instructions on how to add a new architecture port to IeeeCC754++. Finally, Appendix C lists some reference material such as the command line options of IeeeCC754++, the error codes used within IeeeCC754++, and reference files for the evaluation and optimisation frameworks.

## Chapter 1

# Floating-point numbers, standards, and the user environment

The basics of floating-point arithmetic as an approximation for real-valued arithmetic can be introduced with a simple description in just a few words: Given some base  $\beta$ , a number x is represented with a sign  $S_x$ , a significand  $s_x$ , and an exponent e such that

$$x = S_x \times s_x \times \beta^e. \tag{1.1}$$

However, making such an arithmetic reliable, fast, and portable is far from simple. Between the 1960s and the 1980s, vast numbers of different floatingpoint arithmetics were designed and implemented on a wide range of computing platforms, all of them handling issues like binary formats, rounding, overflow, and underflow, in individual and often incompatible manners. Porting numerical code to another platform and verifying the correctness of the resulting program was a highly complex and time-consuming process. This situation led W. Kahan to write his article "Why do we need a floating-point standard?" [Kah81] in which he underlines the need for a common standard that could be both useful for programmers and practical for implementers. Furthermore, he explains the rationale behind the standard draft which was proposed in 1981 after three years of work in the corresponding IEEE subcommittee. It still took another four years of work and discussions to finally release the standard as IEEE 754 in 1985.

In this chapter, we introduce the basic ingredients for the following chapters: floating-point numbers and some of their basic properties, the main IEEE standard concerning floating-point numbers (IEEE 754-2008 and its former incarnations), and what we call the "user's environment": the programming and execution environment a programmer experiences when writing numerical code using floating-point numbers on a given platform. Furthermore, we take a look at what is actually available to the programmer in a given user environment (on some hardware platform).

# 1.1 The foundation: Floating-point numbers

As [Mul<sup>+</sup>10, p. xv] notes, "floating-point arithmetic is by far the most widely used way of approximating real-number arithmetic for performing numerical calculations on modern computers." Consequently, a vast selection of material on floating-point arithmetic has been written, including excellent introductions and comprehensive treatises. To avoid giving yet another introduction to floating-point arithmetic, we only introduce floating-point numbers and their features as far as they are needed in this thesis, and refer to [Gol91] and e.g. [Mul<sup>+</sup>10] for more detailed treatise. As **IeeeCC754++** is based on **IeeeCC754**, most of the notation used in this thesis is borrowed from [VCV01a] and [VCV01b].

Let  $\mathbb{F}(\beta, t, L, U)$  be the set of floating-point numbers in base  $\beta \ge 2$ , precision t > 0, and exponent range [L, U] with L < U. Every floating-point number  $x \in \mathbb{F}(\beta, t, L, U)$  consists of a sign  $S_x \in \{-1, 1\}$ , a significand<sup>1</sup>  $s_x = x_0.x_1x_2...x_{t-1}$  (which has t digits), and an exponent  $e_x \in [L, U]$ . In this thesis, we will only consider the case  $\beta = 2$ .

Floating-point representations of a number  $x \in \mathbb{F}(\beta, t, L, U)$  are not necessarily unique: For example, both  $0.01 \times 10^1$  and  $1.00 \times 10^{-1}$  represent the number 0.1 in  $\mathbb{F}(10, 3, -1, 1)$ . Setting  $x_0 \neq 0$  makes the representation of x unique and is called normalisation of x. For  $\beta = 2$ , this is equivalent to setting  $x_0 = 1$ . This means that all floating-point numbers in  $\mathbb{F}(2, t, L, U)$  with exponent  $e_x \in [L, U]$ are normalised, i.e.  $x_0 = 1 \Rightarrow s_x = 1.x_1x_2...x_{t-1}$ .

The value of a normalised floating-point number  $x \in \mathbb{F}(2, t, L, U)$  is then given by

$$x = S_x \times s_x \times \beta^{e_x} = S_x \times \sum_{i=0}^{t-1} x_i 2^{e_x - i}$$

=  $S_x \times 1.x_1 x_2 \dots x_{t-1} \times 2^{e_x}.$  (1.2)

One must be aware of one drawback of using normalisation: 0 cannot be expressed as a normalised number. This can be solved by reserving a special exponent to represent 0. The most common choice (and that of IEEE 754) is  $e_x = L - 1$ ; see page 9.<sup>2</sup>

Given fixed precision and exponent range,  $\mathbb{F}(\beta, t, L, U)$  obviously contains only a finite number of floating point numbers.  $\mathbb{F}(\beta, t, L, U)$  is not closed, i.e. if

<sup>&</sup>lt;sup>1</sup>The significand has also been called mantissa.

<sup>&</sup>lt;sup>2</sup>Usually,  $e_x = 0$  is chosen, resulting in 0 < L < U. This is mainly due to technical reasons: In most cases, the exponent is encoded as an integer bitstring. To allow for negative exponents, common approaches like two's complement representation are avoided for performance reasons. Instead, an appropriate *bias* is chosen that divides the bitstring into positive and negative numbers and that can be decoded by using simple and therefore fast bit shifts. For details and further reasons for choosing L - 1 = 0, see page 9.

$x, y \in \mathbb{F}(\beta, t, L, U)$ , the result  $z = x \land y$  of an operation  $\land$  does not necessarily lie in  $\mathbb{F}(\beta, t, L, U)$  for one of the following reasons:

- z is too large (in magnitude) to be represented, i. e.  $z > \sum_{i=0}^{t-1} (\beta 1) \beta^{U-i}$ . This is called *overflow*.

- z is smaller (in magnitude) than the smallest representable number in  $\mathbb{F}(\beta, t, L, U)$ , i.e.  $0 < |z| < (\beta 1) \times \beta^L$ . This is called *underflow*; z is then called *subnormal* or *tiny*.<sup>3</sup>

- z needs more than t digits to be represented. This might be the case because z needs an infinite number of digits (consider e.g. transcendental numbers like  $\pi$  or periodic numbers like  $\frac{1}{3}$  for  $\beta = 10$  or  $0.1_{10}$  for  $\beta = 2$ ) or because the representation of z in base  $\beta$  is finite, but z lies between two numbers representable in  $\mathbb{F}(\beta, t, L, U)$ . In the latter case, z effectively belongs to  $\mathbb{F}(\beta, r, L, U)$  for some r > t.

To implement a closed version  $(\mathbb{F}^*(\beta, t, L, U), \bigotimes)$  of  $(\mathbb{F}(\beta, t, L, U), \vartriangle)$ , all three of the mentioned cases need to be addressed:

- Overflow might naively be handled by setting z to the largest representable normalised number. However, this is dangerous as it might introduce an error of arbitrary magnitude. More commonly, some kind of exception or a special value to represent  $\infty$  (or both) are utilised to notify the user of potential problems and provide some meaningful insight. A common choice for a representation of a special value is using an exponent of U + 1.

- In case of underflow, the easiest approach is to simply set the significand of the resulting value to zero (i. e. z = 0, called *flush to zero*). This introduces an error of magnitude  $\mathcal{O}(\beta^L)$ .

Another approach is to use the special exponent L-1 (also commonly used for representing 0, see above) to represent z without normalising the significand, thus making use of all potential values of the significand. This fills the gap between 0 and the smallest representable (normalised) floatingpoint number with evenly spaced numbers, effectively decreasing the error to a magnitude of  $\mathcal{O}(\beta^{L-t+1})$ .

In both approaches, an additional exception might be raised to notify the user.

• In the case of z lying between two (adjacent) floating-point numbers  $z_1, z_2 \in \mathbb{F}(\beta, t, L, U), z$  must be *rounded* to either x or y. For a discussion of rounding strategies, see page 10. The error introduced by rounding is of magnitude  $\mathcal{O}(\beta^{1-t})$ . More precisely, the following holds for the relative error  $\epsilon(x)$ :

<sup>&</sup>lt;sup>3</sup>Historically, z has also been called *denormalised*.

$\epsilon(x) \leq \frac{1}{2}\beta^{1-t}$  in round to nearest mode, and  $\epsilon(x) \leq \beta^{1-t}$  for the other rounding modes, cf. Section 1.3 and [Mul+10, pp. 23 sq.].

For actual implementations, the issue of illegal operations has to be handled. Given  $x \in \mathbb{F}(\beta, t, L, U)$ , consider e.g. x/0 or  $\sqrt{x}$  for x < 0 whose result is not defined. Common approaches are to raise an exception and/or to return a special value (usually called NaN = Not a Number) to notify the user that no proper floating-point number can be returned. Furthermore, the propagation of values like NaN or  $\infty$  (if used) has to be considered. In the next section, we discuss the way IEEE 754-2008 handles these issues.

In the following, we will denote the extended set of floating-point numbers with base  $\beta \ge 2$ , precision t > 0, and exponent range [L-1, U+1], 0 < L < U, by  $\mathbb{F}^*(\beta, t, L, U)$ , which includes the special exponents L-1 and U+1 to represent values of  $0, \infty$ , and NaNs.

# 1.2 The standards: IEEE 754 and 854

In this section, we present the requirements that the "IEEE Standard for Floating-Point Arithmetic" IEEE 754-2008 demands from conforming floating-point implementations. Starting with the first revision of this standard, IEEE 754 [IEEE85], we present the main principles and concepts of this standard which introduced strict requirements for conforming floating-point implementations for the first time. In order to understand the state of some current implementations and their conformity to the (current) standard, we then discuss the small additions done in the second revision, IEEE 854 [IEEE87], and in more detail the current incarnation of the standard, IEEE 754-2008 [IEEE08]. Finally, we briefly comment on the revision that is currently ongoing to produce IEEE 754-2018.

### 1.2.1 IEEE 754

When IEEE 754 was released as "IEEE Standard for Binary Floating-Point Arithmetic" in 1985 after years of work, it stated its rationale in the foreword: "This standard defines a family of commercially feasible ways for new systems to perform binary floating-point arithmetic. The issues of retrofitting were not considered." [IEEE85] It aims at providing a sane and understandable way of performing floating-point operations in a well-defined floating-point arithmetic, while at the same time enabling this arithmetic to be implemented in a costefficient manner. And, as [Mul<sup>+</sup>10] notes, it indeed "was a key factor in improving the quality of the computational environment available to programmers."

Nowadays, virtually all processor designs, compilers, and mathematical libraries implement IEEE 754 (at least to some extent) and provide for a predictable computing environment for programmers designing numerical software.

In the following, we explain how IEEE 754 addresses the issues raised in the previous section.

#### Representations

IEEE 754 starts by specifying two binary number formats for floating-point calculations, the so-called "basic formats" single precision and double precision. Conforming implementations must implement at least the single format.

Furthermore, it defines two extended formats which can be used for intermediary computations to achieve better accuracy compared to when using target precision in intermediary computations. The standard recommends the use of an extended format for the widest implemented precision only. In practice, this means that most platforms implement single, double, and double-extended precision.

The basic formats make use of the base being  $\beta = 2$ : The first digit of every normalised number's significand is always equal to 1, whereas the first digit of a subnormal number is 0. Given a way to distinguish between normalised and subnormal numbers without looking at the significand (which is possible in IEEE formats, see below), this first digit needs not be explicitly stored but is implied. Due to this clever implementation, the length of the significand is increased by one bit. The implicitly stored bit is called *hidden bit*.

Given a floating-point number  $x = S_x \times s_x \times e_x \in \mathbb{F}^*(2, t, L, U)$ , IEEE 754 reserves the extremal values L - 1 and U + 1 of the exponent  $e_x$  for special values:

- If  $e_x = L 1$  and the significand  $s_x = 0$ , then x is a signed zero (depending on the value of the sign  $S_x$ ).

- If  $e_x = L 1$  and  $s_x \neq 0$ , then x is a subnormal number.

- If  $e_x = U + 1$  and  $s_x = 0$ , then x is *infinite*, i. e.  $x = S_x \cdot \infty$ .

- If  $e_x = U + 1$  and  $s_x \neq 0$ , then x is not a number, i. e. it is an NaN.

Additionally, the exponent is stored as a *biased exponent* with bias b, meaning that, when interpreting the stored exponent  $E_x \in [0, 2^q - 1]$  of q bits length as an unsigned integer, the value  $e_x$  of the exponent is interpreted as follows:

- If  $E_x = 0$  (= L 1), then x is a signed zero or a subnormal number.

- If  $E_x = 2^q 1$  (= U + 1), then x is an infinity or an NaN.

- If  $0 < E_x < q-1$ , then x is a normalised number with exponent  $e_x = E_x b$ .

The bias is then given by  $b = 2^{q-1} - 1$ .

With this floating-point encoding, 0 is represented by a bitstring only containing zeroes (or by a bitstring with a leading one and then followed by all zeroes in case of a negative 0), and it is easy to distinguish between normalised and subnormal

numbers, zeroes, infinities, and NaNs. Furthermore, using a biased encoding for the exponent makes it possible to represent positive and negative exponents without using two's complement or sign-magnitude representations, which would have made comparing floating-point numbers harder. Another advantage is that positive floating-point numbers including +0 and  $+\infty$  are ordered like their binary representation (interpreted as integers). This makes it possible to obtain the next floating-point number (i. e. the floating-point successor) by interpreting the binary representation of a floating-point as an integer and adding one to that integer.

Given these representations, IEEE 754 defines the following formats:

- Single precision: 32 bits wide, with 1 sign bit, 8 bits for the exponent, and 23 bits for the significand. This means the following values are used: t = 24 with hidden bit, L = -126, U = 127, b = 127, i. e. the standard implements  $\mathbb{F}^*(2, 24, -126, 127)$ .

- Double precision: 64 bits wide, with 1 sign bit, 11 bits for the exponent, and 52 bits for the significand. This means the following values are used: t = 53 with hidden bit, L = -1022, U = 1023, b = 1023 i.e. the standard implements  $\mathbb{F}^*(2, 53, -1022, 1023)$ .

- Single-extended:  $p \ge 32$ , hidden bit optional,  $L \le -1022$ ,  $U \ge 1023$ .

- Double-extended:  $p \ge 64$ , hidden bit optional,  $L \le -16382$ ,  $U \ge 16383$ .

As a side note, we give the definition of the most widely used double-extended format which is implemented in Intel's x87 floating-point unit (cf. Section 5.2.1):

• Intel x87 double-extended: 80 bits wide, with 1 sign bit, 15 bits for the exponent, and 64 bits for the significand. This means the following values are used: t = 64 without hidden bit, L = -16382, U = 16383, b = 16383 or  $\mathbb{F}^*(2, 64, -16382, 16383)$ .

#### **Rounding modes**

As discussed in Section 1.1, the result of an operation involving floating-point numbers does not necessarily lie in the set of representable floating-point numbers in the target format. If the precise result is a valid real number, it can be *rounded* to a permissible floating-point number: "Rounding takes a number regarded as infinitely precise and, if necessary, modifies it to fit in the destination's format." [IEEE85]. IEEE 754 defines four rounding modes: the default rounding mode round to nearest and three directed rounding modes round toward  $+\infty$ , round toward  $-\infty$ , and round toward 0:

• In round to nearest mode, "the representable value nearest to the infinitely precise result shall be delivered". If the magnitude of the precise result is at

least  $2^{U}(2-2^{-t})$ , an infinity with no change in sign is returned. If the precise result lies exactly between two representable floating-point numbers, the number with the least significant bit zero is returned (tie to even). Therefore, this rounding mode is also called *round to nearest even*.

In the three other modes, the number closest to and no less (round toward +∞), no greater (round toward -∞), or no greater in magnitude (round toward zero) than the infinitely precise result is returned.

#### Operations

IEEE 754 defines a set of operations on floating-point numbers and mandates that conforming implementations return correctly rounded values for these operations. Correctly rounded means that each operation must be performed as if it first produced an intermediate result correct to infinite precision and with unbounded range, and then this intermediate result is rounded to the target format according to the currently selected rounding mode. Care has to be taken to cover  $\pm 0$ , infinities, and NaNs; furthermore, IEEE 754 defines "exceptions caused by exceptional operands and exceptional results", see below.

The operations can be categorised into the following groups:

- Arithmetic operations: These include addition, subtraction, multiplication, division, remainder, and square root. In the following, they are also referred to as *basic operations*.

- Conversion operations. The following conversions must be supported:

- Conversions between all supported floating-point formats. Conversion to a wider format is always exact; conversions to a narrower format must be rounded.

- Conversion operators between all supported floating-point and integer formats must be provided.

- Rounding a floating-point number to integral value: A given floating-point number is rounded so that it is exactly convertible to an integer. It is stored in the same floating-point format as the original number.

- Conversion between binary numbers and decimal representations (also known as binary to decimal conversion and vice versa): To interpret numerical values given as binary floating-point numbers or to input numerical values into a floating-point program, a conforming implementation must provide conversion routines between the supported floating-point formats and a decimal representation. At the time of releasing the standard, efficient algorithms to perform these conversions were not yet known (see [Mul+10, pp. 43 sqq.]). Therefore, IEEE 754

mandates that these conversions are to be correctly rounded only for certain ranges of numbers. For details, see [IEEE85, pp. 7 sq.].

• Comparisons: It must be possible to compare floating-point numbers in all supported formats. Comparisons are always exact. To enable handling of NaNs when comparing floating-point numbers, IEEE 754 introduces the relation *unordered* to describe comparisons between NaNs and any other floating-point number. The usual relations like equal, greater than, equal greater than etc. are available. The sign of a zero is ignored when comparing.

When one of the operands is an infinite value or an NaN, special rules apply:

- Infinities are interpreted as limiting cases for real arithmetic, i. e.  $-\infty < x < \infty$  with  $x \in \mathbb{F}(\beta, t, L, U)$ . Arithmetic on infinite operands is performed in this sense; it is always exact.

- IEEE 754 distinguishes between two types of NaNs: signalling and quiet NaNs. If an operand is a quiet NaN, it is propagated by all operations. If an operation encounters a signalling NaN, the invalid exception (see below) is signalled and a quiet NaN is returned.

It should be noted that a few additional "helper" functions are recommended, such as **copy**, **negate**, **abs**, and **class**. As these only serve more technical purposes and are not influenced by rounding or exceptions, they are of no further relevance in this thesis.

#### **Exceptions and traps**

When executing operations on floating-point numbers, it is not always possible that the result of the given operation yields a floating-point number representable in the target format or that it is a number at all. Consider e.g. division by 0 or computing a square root of a negative number. In order to enable the user to appropriately handle exceptional circumstances arising during a floating-point computation, IEEE 754 defines "five types of exceptions that shall be signalled when detected" [IEEE85]. It allows for two types of signals: either setting an appropriate status flag or taking a trap. While it must be possible for the user to catch these traps, the default is to continue without trapping. The status flag must collect all exceptions that happened since the last reset of its contents; such a reset must be initiated by the user. This way of handling the status flags enables the user to control the program's behaviour even in the presence of exceptions. IEEE 754 defines the following five exceptions:

• Invalid operation: This exception is signalled if an operand is invalid for the operation to be performed. This includes the divisions 0/0 and  $\infty/\infty$ , the multiplication  $0 \times \infty$ , taking a square root of a number less than zero,

certain comparisons between unordered operands, magnitude subtraction of infinities, and a few more. For a complete list, see [IEEE85, p. 11].

When an invalid exception occurs, a quiet NaN is returned for operations with a floating-point target format.

- Division by zero: "If the divisor is zero and the dividend is a finite nonzero number, then the division by zero exception shall be signalled. The result, when no trap occurs, shall be a correctly signed  $\infty$ ."

- Overflow: "The overflow exception shall be signalled whenever the destination format's largest finite number is exceeded in magnitude by what would have been the rounded floating-point result were the exponent range unbounded." When no trap occurs, the result is determined by the rounding mode and the sign of the intermediate result. For trapped overflow, IEEE 754 aims to preserve as much information from the operation as possible by requiring the implementation to include as many sensible bits as possible. For details on the returned result, see [IEEE85, p. 11].

- Underflow: When a result in the subnormal range is returned, i. e. its absolute value is less than  $2^L$ , in many cases the result is exact (cf. [Mul+10, p. 124]). However, in some circumstances, a significant loss of accuracy can occur. IEEE 754 defines two events which contribute to an inaccurate very small result: loss of accuracy and tininess (i. e. a subnormal number is returned). Tininess can be detected either before or after rounding, whereas loss of accuracy can be detected when the result differs from what would have been attained were either the exponent range unbounded or the exponent range and the precision unbounded.

In [Cuy<sup>+</sup>02], the three cases are categorised as follows: For an arithmetic operation  $x \otimes y$  with  $x, y \in \mathbb{F}^*(\beta, t, L, U)$ , let  $r_e$  be the exact result (unbounded precision and unbounded exponent range),  $r_t$  the normalised result rounded to a precision of t digits (with unbounded exponent range), and  $r \in \mathbb{F}^*(\beta, t, L, U)$  the returned result (which might be a subnormal number). Then,

- *u-underflow* occurs when  $|r_t| < \beta^L$  and  $r \neq r_t$ ,

- *v*-underflow occurs when  $|r_t| < \beta^L$  and  $r \neq r_e$ , and

- w-underflow occurs when  $|r_e| < \beta^L$  and  $r \neq r_e$ .

Note that u-underflow always implies v-underflow (since denormalisation loss implies inexactness), and v-underflow implies w-underflow (since tininess after rounding implies tininess before rounding).

In absence of an underflow trap, the underflow exception is only signalled when both tininess and loss of accuracy occur; with trapped underflow, it is signalled when tininess is detected, and similar to the overflow case, a result is returned that preserves as much information as possible (cf. [Mul+10]).

• *Inexact*: To cite IEEE 754 once more, "If the rounded result of an operation is not exact or if it overflows without an overflow trap, then the inexact exception shall be signalled. The rounded or overflowed result shall be delivered to the destination or, if an inexact trap occurs, to the trap handler."

It should be noted that of these exceptions, only overflow with inexact and underflow with inexact can occur at the same time.

If a trap handler is implemented to allow direct reaction to exceptional circumstances, the standard requires it to be a "subroutine-like function" that provides the user with information about the type of exception that occurred, the operation, as well as the destination format. For underflow, overflow, and inexact, the correctly rounded result, possibly including additional information (see above), needs to be returned; for invalid and divide by zero, the operand values must be supplied by the trap handler.

#### Miscellaneous

IEEE 754 concludes with Annex A that recommends a number of functions and predicates as "aids to program portability across different systems". These include functions to copy the sign of one operand to another operand or to generate the next representable floating-point number of an operand, classification functions to find out whether an operand is finite or an NaN, and additional comparison functions.

#### 1.2.2 IEEE 854

IEEE 754 deals only with binary floating-point numbers, i. e. with base  $\beta = 2$ . However, most of the principles described in the standard can also be applied to arbitrary bases. Therefore, two years later a new standard called "IEEE Standard for Radix-Independent Floating-Point Arithmetic" was published as IEEE 854. It allows for bases  $\beta = 2$  and  $\beta = 10$  by generalising all definitions that formerly only applied to  $\beta = 2$ . Furthermore, a few clarifications were added.

The differences between both standards from a practical point of view can be best summarised by citing the foreword of IEEE 854: "The committee believes that, except for a possible conflict with the requirements in 5.6 and 7.2 that unrecognisable decimal input strings signal an exception, and in 6.3 that the sign of zero be preserved in certain conversion operations, any implementation conforming to ANSI/IEEE Std 754-1985 will also conform to this standard. In addition, the definition of logb has been enhanced in the Appendix, and two new functions, conv and nearbyinteger, have been added."

#### 1.2.3 IEEE 754-2008

After publication of IEEE 754 and IEEE 854, the new standard was widely adopted. While not all designers of floating-point hardware and software implemented all features required by IEEE 854, e. g. providing only one rounding mode (usually round to nearest) or not supporting exceptions, the new standard raised the bar for floating-point implementations considerably and succeeded especially in providing standard formats, exceptions, and rounding modes, as well as requiring the basic operations to be rounded correctly. Virtually all floating-point arithmetic since IEEE 754 has been implemented adhering to its basic principles and incorporating most of its requirements, leading indeed to better portability, comprehensibility, and reliability of numerical algorithms.

Approaching the end of the last millennium, it was deemed necessary to revise the standard in order to merge IEEE 754 and IEEE 854, extend the old standards where necessary, and render some definitions and requirements more precise (e.g. conversion from binary to decimal representation). The revision process started in 2000 and culminated in the approval of the "IEEE Standard for Floating-Point Arithmetic", also called IEEE 754-2008, on 12 June 2008.

It is important to note that not only did the principal design goals (numerical robustness, reliability, and portability) remain the same, but that it was aimed to provide a standard that still accepted all platforms as conforming that conformed to IEEE 754 and IEEE 854, i.e. the new standard should not invalidate any hardware that conformed to its older versions [Mul<sup>+</sup>10, p. 79].

That being said, the revision provided for the opportunity to reformulate the standard's principles in a more precise manner, while at the same time accounting for advances in floating-point design and the underlying numerical methods by requiring or recommending new operations and alternative exception handling facilities. Citing from its foreword, "This standard provides a discipline for performing floating-point computation that yields results independent of whether the processing is done in hardware, software, or a combination of the two. For operations specified in the normative part of this standard, numerical results and exceptions are uniquely determined by the values of the input data, the operation, and the destination, all under user control." The foreword ends by expressing hope "that language designers will look on the full set of operation, precision, and exception controls described here as a guide to providing the programmer with the ability to portably control expressions and exceptions. It is also hoped that designers will be guided by this standard to provide extensions in a completely portable way." [IEEE08]

IEEE 754-2008 consists of two parts: a *normative* part that conforming implementations must adhere to, and a *recommendatory* part that describes operations and facilities that provide for better numerical results and better portability. The standard notes what is needed for an implementation to be called conforming: A "programming environment" must support the required operations, formats, and features of the normative part in either of the two supported bases  $\beta = 2$  or  $\beta = 10$ . It goes on by listing some programming environment considerations: "Conformance to this standard is a property of a specific implementation of a specific programming environment, rather than of a language specification." [IEEE08]

#### Formats

IEEE 754-2008 distinguishes between basic, interchange, extended, and extendable formats. It defines three binary basic formats called binary32, binary64, and binary128, as well as two decimal basic formats (in binary representation, called decimal32 and decimal64). Interchange formats are fixed-width encodings that can be used for the exchange of floating-point data between implementations; they are identified by their size. An extended precision format extends a basic format by using a representation with both larger exponent range and a longer significand. For an extendable precision format, the range and length of the significand can be specified by a user.

A conforming implementation must at least implement one of the basic formats with means to initialise this format and convert values between that format and all other supported formats, and a corresponding interchange format with means to read and write that format. Furthermore, the required operations for the implemented basic format(s) must be supported.

It should be noted that IEEE 754-2008 does not define completely new formats. In fact, binary32 is IEEE 754's single format, and binary64 is IEEE 754's double format. Furthermore, Intel's x87 double-extended 80 bit format is called binary64 extended in IEEE 754-2008. While most programming languages do not offer extendable formats, additional floating-point libraries can support such formats, such as MPFR (see Section 5.7.3 and [GNU16d]). Table 1.1 lists the formats used in this thesis as well as their names. For historical reasons and the current naming conventions in programming languages, the "old" names such as single and double will be used instead of binary32 and binary64.

| Format           | Name      | Width | Exponent | Significand    | Exponent bias        |

|------------------|-----------|-------|----------|----------------|----------------------|

| binary16 half 16 |           | 5     | 11       | $2^4 - 1 = 15$ |                      |

| binary32         | single    | 32    | 8        | 24             | $2^7 - 1 = 127$      |

| binary64         | double    | 64    | 11       | 53             | $2^{10} - 1 = 1023$  |

| binary128        | quadruple | 128   | 15       | 113            | $2^{14} - 1 = 16382$ |

| binary64 ext.    | extended  | 80    | 15       | 64             | $2^{14} - 1 = 16382$ |

**Table 1.1:** (Binary) Floating-point formats. Partly taken from [WIK17q]. Width, exponent, and significand are given in bits; with the exception of the extended format, the significand includes the hidden bit.

#### Attributes and Rounding

IEEE 754-2008 defines attributes that are "logically associated with a program block to modify its numerical and exception semantics. A user can specify a constant value for an attribute parameter" [IEEE08, p. 15]. In particular, these are rounding-direction attributes, alternate exception handling attributes (which both existed in the former standards, albeit without being called attributes), preferred width attributes, value-changing optimisation attributes, and reproducibility attributes. The standard mandates that rounding-direction attributes must be supported.

For binary floating-point arithmetic, the four rounding modes described in IEEE 754 remain in IEEE 754-2008 as they are. Additionally, when rounding to nearest, a new tie-breaking rule is added, leading to a new rounding mode *round to nearest, ties to away*: When an exact value lies exactly between two representable floating-point numbers, the one with larger magnitude is returned. This rounding mode is especially relevant for decimal floating-point arithmetic as this introduces the so-called "kaufmännische Rundung" [DIN92]. For binary implementations, it is not required. Table 1.2 lists the rounding modes and their respective attribute names which will be used in this thesis.

| IEEE 754-2008 rounding-direction attribute | IEEE 754 rounding mode |  |  |  |

|--------------------------------------------|------------------------|--|--|--|

| roundTiesToEven                            | round to nearest       |  |  |  |

| roundTiesToAway                            |                        |  |  |  |

| roundTowardPositive                        | round toward $+\infty$ |  |  |  |

| roundTowardNegative                        | round toward $-\infty$ |  |  |  |

| roundTowardZero                            | round toward 0         |  |  |  |

Table 1.2: Rounding modes and attributes.

#### Operations

IEEE 754-2008 clarifies some of the operations listed in the former standards, especially concerning comparisons, and adds new required functions like nextUp, nextDown, minNum, and maxNum. Additionally, some formerly recommended functions like copy, negate, abs, or copySign are now mandatory. For decimal floating-point arithmetic, some specialised operations like sameQuantum and quantize are added, as well as preferred exponents for decimal results for all operations.

From an arithmetic point of view, the most notable change with regard to required operations is the incorporation of the fusedMultiplyAdd (fma) operation which has found its way into numerous processor designs as many scientific workloads require the multiplication of two values directly followed by an addition. IEEE 754-2008 mandates  $fma(x, y, z) = (x \times y) + z$  to be calculated with unbounded range and precision, and rounded only once to the destination format.

Concerning conversion between binary floating-point numbers and decimal representations, IEEE 754-2008 requires correctly rounded base conversions for all possible values. This is a stricter requirement compared to the older standards (cf. page 11).

At the time when IEEE 754 and IEEE 854 were published, efficient algorithms and implementations for trigonometric, exponential, and logarithmic functions were not known, so these operations were not mentioned at all in these standards. Although at the time of the revision process enough knowledge and computing power was available to implement and compute correctly rounded versions of these operations in an efficient manner (cf. e. g. [Lau08]), they were only added to IEEE 754-2008 as recommended operations, including definitions for special cases.

Furthermore, IEEE 754-2008 recommends reduction operations that take a vector of operands in one format and return a result in the same format, thus reducing a vector of operands into a single result. These operations include e.g. sum, dot, sumSquare, sumAbs, or scaledProd and are recommended for all supported arithmetic formats.

#### **Exceptions and infinity arithmetic**

With regard to exceptions and arithmetic with special values such as infinities and NaNs, the definitions of the older standards were revised and clarified, but no substantial changes were introduced.

The clause about alternative exception handling was extended to allow optional exception handling in various forms, including traps and other models such as try/catch [WIK16].

#### Reliability and portability

To facilitate better reliability and portability of numerical programs, IEEE 754-2008 adds some clauses to address different facets of modern programming languages and compilers, such as expression evaluation rules, assignments, function values, and optimisations. It recommends guidelines and principles to handle these in portable manners. Furthermore, it adds optional preferredWidth attributes which can be used to change the format of intermediate computations for program blocks. This enables the user to increase the intermediate precision for accuracy-sensitive parts of an algorithm.

Furthermore, a clause was added dedicated to the reproducibility of floatingpoint computations. It notes that "reproducible results require cooperation from language standards, language processors, and users" [IEEE08, p. 51] and suggests means to control how floating-point operations are (reproducibly) performed.

Finally, IEEE 754-2008 concludes with Annex B about program debugging support, giving guidelines about which features are needed from a debugger to efficiently find numerical bugs in a floating-point program.

This overview of IEEE 754-2008 concentrated on the main differences to its earlier versions IEEE 754 and IEEE 854 as far as they are needed for this thesis. For an overview of the revision process and a more detailed analysis see [WIK16]; for detailed information about the entire standard, the reader is referred to the revision website [Hou08].

#### 1.2.4 IEEE 754-2018

According to the rules of the IEEE, standards have a limited validity of 10 years. After this period, the standard must either be revised or withdrawn, otherwise it is assigned an inactive status (see [IEEE17b]). To maintain a valid active floatingpoint standard, IEEE 754-2008 needs to be revised by 2018. Therefore, mid-2015 "a minor revision has been undertaken, to clean up its errata and republish it mostly unchanged" [Hou17b]. During the first meeting, the scope of this minor revision was explicitly stated as follows: "The scope of this activity is to produce a timely correction to the 2008 standard, fixing errors and ambiguities and avoiding major restructuring, additions, deletions, changes in behaviour, or other controversial actions." [Hou15] It is intended to start a more thorough revision process in 2019 towards producing the next iteration (tentatively called IEEE 754-2028).

The list of errata of IEEE 754-2008 has been chosen as a starting point for the current revision [IEEE17a], with additional topics being raised during meetings. The most notable topics discussed for IEEE 754-2018 so far are unifying the use of the terms function, operation, and predicate, special cases for the pown operator<sup>4</sup>, setting minimum values for small extendable formats (precision  $t \ge 3$  and  $U \ge 2$  for  $\beta = 2$ ), and the addition of definitions for asinPi and acosPi<sup>5</sup> (which are missing in IEEE 754-2008). Suggestions deemed to be out of scope for the current process are postponed to IEEE 754-2028.

## 1.3 Rounding and error analysis

Executing numerical computations on any platform with limited precision arithmetic (such as floating-point arithmetic) inevitably leads to errors. [Hig02] mentions three main causes for these errors:

- Rounding errors. These are unavoidable due to the limited precision.

- Data uncertainty. This may stem from measurement or estimation errors when working on "real-world" data, from perturbations while storing or converting the data (which basically comes down to rounding errors), or from earlier computations performed on the original data.

<sup>&</sup>lt;sup>4</sup>pown $(x, n) = x^n$  for  $x \in \mathbb{R}$  and  $n \in \mathbb{N}$ .

<sup>&</sup>lt;sup>5</sup>For  $x \in [-1, 1]$ , these are defined as  $\operatorname{asinPi}(x) = \operatorname{arcsin}(x)/\pi$  and  $\operatorname{acosPi}(x) = \operatorname{arccos}(x)/\pi$ .

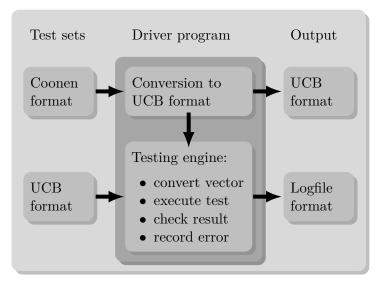

• Truncation (discretisation) errors. These errors are introduced by modelling the problem and choosing an algorithm to perform the calculation. For instance, many standard numerical methods can be derived by taking finitely many terms of a Taylor series. The number of terms used to compute the result directly influences the precision (and thus the error) and the speed of the computation.